KlausST

Advanced Member level 7

Hi,

With inductive loads the rising edge of the voltage comes first, then the rising edge of the current. This seems to be O.K.

But with capacitive loads the rising edge of the current comes first, then the voltage. This seems to cause problems.

Check the hardware signals, check the interrupts and the resulting values..

Klaus

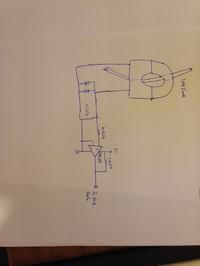

My assumption is that there is a problem in hw or sw with the pf measurement.Using same code/circuit the system sees the fan V,I phase as 43 deg, and 0 for 200W resistive bulb.

I don't know why the system saw cap bank as resistive.

With inductive loads the rising edge of the voltage comes first, then the rising edge of the current. This seems to be O.K.

But with capacitive loads the rising edge of the current comes first, then the voltage. This seems to cause problems.

Check the hardware signals, check the interrupts and the resulting values..

Klaus