KlausST

Advanced Member level 7

Hi,

to get the information about the complex impedance of the load you need to simultaneously sample "voltage" and "current".

How many samples: Nyquist says at least twice the signal frequency. I recommend at least 4 samples per period. With 10MHz this means 40 Msamples/second. (are you able to do this?)

******

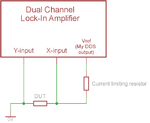

As i wrote before a lock in amplifier is far more simple. I used simple analog switches. then some Rs and Cs as low pass filters. The ADC can be very slow, because it simply has do measure about DC.

******

Anyway 10MHz is not that simple. Not with high speed ADC, nor with lock in amplifier. Expect a lot of error. In either case it needs a lot of experience to find the errors and cancel/calibrate them.

Klaus

to get the information about the complex impedance of the load you need to simultaneously sample "voltage" and "current".

How many samples: Nyquist says at least twice the signal frequency. I recommend at least 4 samples per period. With 10MHz this means 40 Msamples/second. (are you able to do this?)

******

As i wrote before a lock in amplifier is far more simple. I used simple analog switches. then some Rs and Cs as low pass filters. The ADC can be very slow, because it simply has do measure about DC.

******

Anyway 10MHz is not that simple. Not with high speed ADC, nor with lock in amplifier. Expect a lot of error. In either case it needs a lot of experience to find the errors and cancel/calibrate them.

Klaus