David_

Advanced Member level 2

Hello.

This is the first post of a thread that will be running for a long time, though I can for see that I will erratically pop in and out but I am dead set on achieving the goal of this project so no matter how dead the thread may seem I will be back.

I can't give you all the details you would want because I don't know them my self yet, to begin with this thread will deal with a few system design problems much like my first question which will follow shortly(it ended up as kind of a long post).

But I want to design a LCRZ-meter that will be connected through a isolated USB bus to a PC running Matlab(later a LCD shall be added to enable stand-alone operation but that is something that will be added when the meter is functional), the main feature of this meter is to be able to plot impedance vs frequency over a adjustable range(or something else vs frequency. But the maximum frequency range is going to be 10/50Hz up to 1MHz. I also have a ambition to enable a adjustable(and optional) DC-bias to be used to aces the DC currents effect on inductor cores and the DC voltages effect on ceramic capacitors.

Specifications(thus far):

Excitation Signal Frequency range: 50Hz(or 10Hz if there are any point in starting there) to 1MHz.

Excitation Signal Amplitude: 1Vp-p to 20Vp-p.

Excitation Signal Output Current: 1A(I suppose that would have to be ±1A).

The problem with that output current is that I want to make this a battery driven device, but at ebay they sell 3,7V Li-Ion AAA batteries with up to 10000mA/h and I don't mind having to use a few of those if that would enable my design to be run on batteries to be charged through USB(I can't plan for it but before this meter is done I am convinced that the USB C connector will have become the standard which means not 5V but 20V, and not 500mA but a few Watts)

Although I have begun discussing the battery situation in another thread so for now lets assume that I got the supply covered.

I have read as much as I can find on this subject, if I haven't been clear about it this meter shall function by using a DDS(AD9954) to generate a sine-wave, that sine-wave is amplified through a PGA/VGA stage and the current boosted some how before it is lead to the DUT.

Then I shall have 1 ADC to read the voltage developed over the DUT, and 1 ADC reading the voltage developed over a precision resistor that is in series with the DUT. The acquisition shall be performed in such a way that I can extrapolate the phase between these two signals, that is one major hurdle to overcome since I haven't figured out how that is done yet(I have begun studying complex numbers). I know that with these 3 peace's of information I can calculate everything from impedance to inductance to ESR, how that is done is a entirely different matter... But even though I may be hilariously far off from being able to do that I will not be able to rest in peace before I have learned to do it, and done it.

In any case I have thought to enable a user adjustable output voltage even if I am currently unsure about what that will give me, but being able to choose a 20Vp-p excitation signal has to to some extent enable the measurement of a smaller impedance, I think anyway, it sounds reasonable, as opposed to a maximum of 1,5Vp-p.

But do anyone have any objections or reasons to why I shouldn't use a large adjustable excitation signal amplitude?

I haven't considered how that will effect the acquisition hardware though, I mean I know I am in the need for a gain stage that can be switched between a number of gains, 1x, 10x, 100x & 1000x for example. But since the excitation voltage is so large I need to add a couple or even a few attenuation options as well...

But here comes my actual first question(the question which triggered this thread to be written, as you see there are lots of questions/subjects to cover):

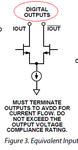

I've got a Complete DDC IC(AD9954) as signal source, that IC has a differential current output(IOUT & -IOUT) and I have found this circuit(for the record it is the only one I have found so far but I have to think there are lots more out there):

To this circuit came this text:

"The current output DAC drives balanced 25-Ω resistive loads, thereby developing an out-of-phase voltage of 0 to +0.5V at each output. This technique is used in lieu of a direct I/V conversion to prevent fast slewing DAC currents from overloading the amplifier and introducing distortion. Care must be taken so that the DAC output voltage is within its compliance rating.

The op-amp is configured for a gain of 2, to develop a final single-ended ground-referenced output voltage of 2-Vp-p. Note that because the output signal swings above and below ground, a dual-supply op amp is required."

But I feel a little insecure about this circuit, the AD9954's output DAC has a compliance voltage range of VDD - 0,5V to

VDD + 0,5V(the DAC is referenced to VDD rather than to GND).

Where VDD is +1,8V, and the combined output current is 15mA(max) and should be limited to 10mA to preserve the output specification/performance(done with a resistor appropriately chosen & connected to separate pin), but what does it mean that the combined output current is set to 10mA?

How do I choose the I/V resistors(the 25Ω resistors in the circuit above)?

Or am I right in thinking that I can do this?:

This is the first post of a thread that will be running for a long time, though I can for see that I will erratically pop in and out but I am dead set on achieving the goal of this project so no matter how dead the thread may seem I will be back.

I can't give you all the details you would want because I don't know them my self yet, to begin with this thread will deal with a few system design problems much like my first question which will follow shortly(it ended up as kind of a long post).

But I want to design a LCRZ-meter that will be connected through a isolated USB bus to a PC running Matlab(later a LCD shall be added to enable stand-alone operation but that is something that will be added when the meter is functional), the main feature of this meter is to be able to plot impedance vs frequency over a adjustable range(or something else vs frequency. But the maximum frequency range is going to be 10/50Hz up to 1MHz. I also have a ambition to enable a adjustable(and optional) DC-bias to be used to aces the DC currents effect on inductor cores and the DC voltages effect on ceramic capacitors.

Specifications(thus far):

Excitation Signal Frequency range: 50Hz(or 10Hz if there are any point in starting there) to 1MHz.

Excitation Signal Amplitude: 1Vp-p to 20Vp-p.

Excitation Signal Output Current: 1A(I suppose that would have to be ±1A).

The problem with that output current is that I want to make this a battery driven device, but at ebay they sell 3,7V Li-Ion AAA batteries with up to 10000mA/h and I don't mind having to use a few of those if that would enable my design to be run on batteries to be charged through USB(I can't plan for it but before this meter is done I am convinced that the USB C connector will have become the standard which means not 5V but 20V, and not 500mA but a few Watts)

Although I have begun discussing the battery situation in another thread so for now lets assume that I got the supply covered.

I have read as much as I can find on this subject, if I haven't been clear about it this meter shall function by using a DDS(AD9954) to generate a sine-wave, that sine-wave is amplified through a PGA/VGA stage and the current boosted some how before it is lead to the DUT.

Then I shall have 1 ADC to read the voltage developed over the DUT, and 1 ADC reading the voltage developed over a precision resistor that is in series with the DUT. The acquisition shall be performed in such a way that I can extrapolate the phase between these two signals, that is one major hurdle to overcome since I haven't figured out how that is done yet(I have begun studying complex numbers). I know that with these 3 peace's of information I can calculate everything from impedance to inductance to ESR, how that is done is a entirely different matter... But even though I may be hilariously far off from being able to do that I will not be able to rest in peace before I have learned to do it, and done it.

In any case I have thought to enable a user adjustable output voltage even if I am currently unsure about what that will give me, but being able to choose a 20Vp-p excitation signal has to to some extent enable the measurement of a smaller impedance, I think anyway, it sounds reasonable, as opposed to a maximum of 1,5Vp-p.

But do anyone have any objections or reasons to why I shouldn't use a large adjustable excitation signal amplitude?

I haven't considered how that will effect the acquisition hardware though, I mean I know I am in the need for a gain stage that can be switched between a number of gains, 1x, 10x, 100x & 1000x for example. But since the excitation voltage is so large I need to add a couple or even a few attenuation options as well...

But here comes my actual first question(the question which triggered this thread to be written, as you see there are lots of questions/subjects to cover):

I've got a Complete DDC IC(AD9954) as signal source, that IC has a differential current output(IOUT & -IOUT) and I have found this circuit(for the record it is the only one I have found so far but I have to think there are lots more out there):

To this circuit came this text:

"The current output DAC drives balanced 25-Ω resistive loads, thereby developing an out-of-phase voltage of 0 to +0.5V at each output. This technique is used in lieu of a direct I/V conversion to prevent fast slewing DAC currents from overloading the amplifier and introducing distortion. Care must be taken so that the DAC output voltage is within its compliance rating.

The op-amp is configured for a gain of 2, to develop a final single-ended ground-referenced output voltage of 2-Vp-p. Note that because the output signal swings above and below ground, a dual-supply op amp is required."

But I feel a little insecure about this circuit, the AD9954's output DAC has a compliance voltage range of VDD - 0,5V to

VDD + 0,5V(the DAC is referenced to VDD rather than to GND).

Where VDD is +1,8V, and the combined output current is 15mA(max) and should be limited to 10mA to preserve the output specification/performance(done with a resistor appropriately chosen & connected to separate pin), but what does it mean that the combined output current is set to 10mA?

How do I choose the I/V resistors(the 25Ω resistors in the circuit above)?

Or am I right in thinking that I can do this?: