sameerdhiman

Member level 5

Actually I measured the resistance of lamp and I found the higher one was 4.7E so I thought using higher resistance (in hundred or kilo range) would make the net effect of lamp resistance negligible.

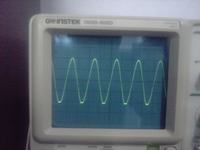

My first attempt gave me much confidence. On 2/Mar/2011 I'll breadboard Wien with FET AGC.

---------- Post added at 13:23 ---------- Previous post was at 13:17 ----------

One more question can I use LPF to lower the ripple effects in AGC loop ?

My first attempt gave me much confidence. On 2/Mar/2011 I'll breadboard Wien with FET AGC.

---------- Post added at 13:23 ---------- Previous post was at 13:17 ----------

One more question can I use LPF to lower the ripple effects in AGC loop ?