Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

In other words, Rdson has a rather large variation range and can be considerably higher than assumed in your simulation.2SK104

N-Channel JFET

Various

field effect transistors,transistors

V(BR)GSS (V)=30

I(D) Abs. Drain Current (A)=20m

I(G) Max. (A)=10m

Absolute Max. Power Diss. (W)=250m

I(GSS) Max. (A)=10n

@V(GS) (V) (Test Condition)=30

V(GS)off Min. (V)=.25

V(GS)off Max. (V)=4.5

@V(DS) (V) (Test Condition)=5.0

@I(D) (A) (Test Condition)=10u

I(DSS) Min. (A)=500u

I(DSS) Max. (A)=12m

@V(DS) (V) (Test Condition)=5.0

I have never seen a SK104 or SK105 datasheet. A summarized specification says:

.........

In other words, Rdson has a rather large variation range and can be considerably higher than assumed in your simulation.

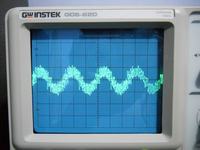

The left waveform is apparently indicating an unstable amplitude control loop.

How do you call a control process that maintains steady oscillations otherwise? I just realized, that the frequency seems to be about 50 Hz, so it may be trivial hum as well.I don`t think that the loop is "unstable"

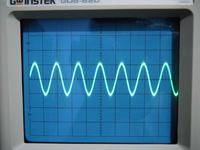

With both waveforms, the timebase is apparently uncalibrated. If the oscillator is working at 1 kHz, then the control signal is "swinging" at about 50 Hz frequency.Can you confirm the following readings?

Output: 10 mV,pp at app 3 kHz

Gate control: 10 mV,pp at app 200 Hz?

If you refer circuit diagram LPF (first order) is configured for 10Hz.

Main Oscillation Frequency: 1KHz

Output frequency from AC-to-DC (Full-wave rectifier): 2 x 1KHz = 2KHz

So the signal at gate should be 2KHz (ripple) riding on 10Hz wave.

Am I correct ?

How do you call a control process that maintains steady oscillations otherwise? I just realized, that the frequency seems to be about 50 Hz, so it may be trivial hum as well.

With both waveforms, the timebase is apparently uncalibrated. If the oscillator is working at 1 kHz, then the control signal is "swinging" at about 50 Hz frequency.

But you should be able to determine the frequency with sufficient accuracy, and e.g. not have to guess about a frequency of 10 Hz if it's actually 50 - 100.Swp. var. (calibrated=no) was adjusted to see the wave otherwise It was shifting.

I am reluctant to call such a loop "unstable", because it is a kind of "instability" which cannot be avoided in a non-linear and discontinuous control loop (caused primarily by the rectification).