ashish_chauhan

Full Member level 5

congrats dear you have done it!!

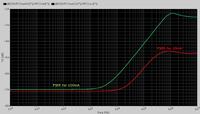

but did u notice the difference between two values of psrr at dc freqs ...

I asked u to run sim for 100mA just for that ... this will provide u some insight in psr behaviour of ldo.

but did u notice the difference between two values of psrr at dc freqs ...

I asked u to run sim for 100mA just for that ... this will provide u some insight in psr behaviour of ldo.