Audioguru

Advanced Member level 7

- Joined

- Jan 19, 2008

- Messages

- 9,461

- Helped

- 2,152

- Reputation

- 4,304

- Reaction score

- 2,011

- Trophy points

- 1,393

- Location

- Toronto area of Canada

- Activity points

- 59,764

You do not make any sense.So when you ADD an inverter, you ADD the HIGH states pulse width? this will equal the inverters delay time

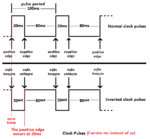

An inverter inverts THE ENTIRE pulse period, not just the positive pulse. If you have a logic IC that is clocked on the positive-going edge and you invert the clock then this logic IC must wait until the positive-going edge (which was the negative-going edge before the pulse period was inverted) occurs. Then the delay time is the pulse width.

I do not know what they use at your work.Why will it mess up the logic? they use them in a circuit at work

If all the other logic is clocked on the positive-going edge but this logic IC has an inverter to delay its clocking a pulse width later then it is clocked AT THE WRONG TIME!

But you do not understand any of this stuff and I do not know why you are asking about it.

If you looked at the datasheets then maybe you will find that all the logic is clocked on a positive-going edge EXCEPT one IC that is clocked on the negative-going edge. Then it has an inverted clock so that it is clocked at the same time as all the other ICs. UNDERSTAND?

I think you are talking about when the clock is inverted?Yes I know The positive edge is 20 microseconds late or delayed from the Non inverted clock

You make no sense. You do not understand ANYTHING about clocked logic.Positive edge going trigger , triggers EVENTS later than Negative edge going trigger

Negative Edge going triggers , triggers EVENTS BEFORE Positive edge going trigger IC chips

You cannot say LATER unless you say the starting point:

1) If the starting point is the negative edge then the positive edge occurs later.

2) if the starting point is the positive edge then the negative edge occurs later.

NOTHING can occur before.