- Joined

- Jul 4, 2009

- Messages

- 16,530

- Helped

- 5,157

- Reputation

- 10,347

- Reaction score

- 5,213

- Trophy points

- 1,393

- Location

- Aberdyfi, West Wales, UK

- Activity points

- 139,765

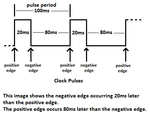

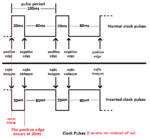

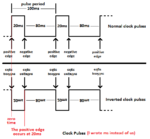

Danny you seem to forget that a time period has to have a starting point. FROM THE SAME REFERENCE STARTING POINT, a circuit operated by say a falling edge may not see that edge for a little longer if the signal is inverted. It's the edge, (the change of level) that matters so if the signal is inverted it will be at the other end of the pulse and hence have a different delay FROM THE REFERENCE POINT.

Brian.

Brian.