zilch

Member level 2

Good day!

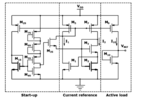

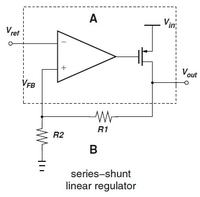

I am currently designing an ultra-low power bandgap reference in 65nm CMOS technology that is supposed to produce reference voltage of at least 200mV. The supply voltage that we initially planned was from the output voltage of a rectifier which is very small. But for now I am using a 0.45V as a supply voltage ( i just assumed that our rectifier will have an output of around 0.45V since we divided the work). But i have doubts regarding my design. Should the transistors operate in saturation region?( my MOS are in cutoff at the moment)

this topology is from https://ieeexplore.ieee.org/xpl/freeabs_all.jsp?arnumber=7217038&abstractAccess=no&userType=inst

I am still thinking of another question haha

I am currently designing an ultra-low power bandgap reference in 65nm CMOS technology that is supposed to produce reference voltage of at least 200mV. The supply voltage that we initially planned was from the output voltage of a rectifier which is very small. But for now I am using a 0.45V as a supply voltage ( i just assumed that our rectifier will have an output of around 0.45V since we divided the work). But i have doubts regarding my design. Should the transistors operate in saturation region?( my MOS are in cutoff at the moment)

this topology is from https://ieeexplore.ieee.org/xpl/freeabs_all.jsp?arnumber=7217038&abstractAccess=no&userType=inst

I am still thinking of another question haha