engr_joni_ee

Advanced Member level 3

- Joined

- Nov 3, 2018

- Messages

- 831

- Helped

- 2

- Reputation

- 4

- Reaction score

- 7

- Trophy points

- 18

- Activity points

- 6,955

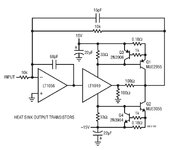

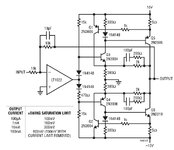

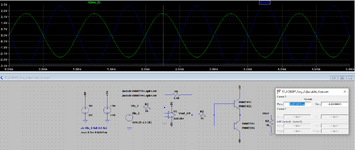

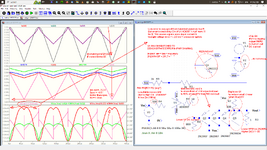

The input to the OpAmp is 0 to 3.3 V. I am using OpAmp in unity gain inverting configuration. The output of the OpAmp will be 0 to -3.3 V. The problem is that the output current of the OpAmp I have selected can not deliver 500 mA if a load is connected. I know that there are OpAmp with higher output current but for some reason, I need to find a solution with FMMT591 OpAmp. One option is to buffer the output using a transistor to increase the output current. I am using PNP at the output of OpAmp. The schematic is attached. Kindly have a look and suggest how can I get 0 to -3.3 V at the load that require 500 mA. Note that the input of the OpAmp will be controlled by DAC/FPGA to get adjustable power supply at the load.

Attachments

Last edited: