yefj

Advanced Member level 5

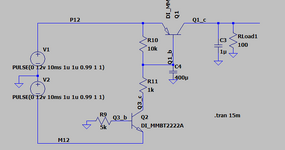

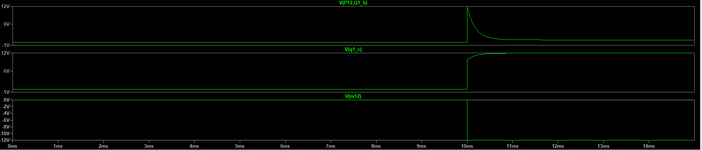

Hello,The circuit is supposed to delay the output of P12 because the PNP is opening gradually.

In previos version it worked great but i put P12 as a pulse and circuit just not working.

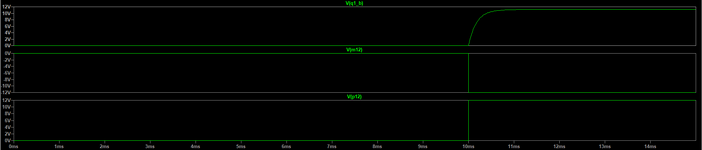

The Veb is totally different.Veb is supposed to be 0 and rise gradually.

But when i made P12 0-12V pulse my Veb is tottaly ruined.

How can i fix it so Veb will rise gradually from 0 till PNP is opening?

LTSPICE file is attached.

Thanks.

In previos version it worked great but i put P12 as a pulse and circuit just not working.

The Veb is totally different.Veb is supposed to be 0 and rise gradually.

But when i made P12 0-12V pulse my Veb is tottaly ruined.

How can i fix it so Veb will rise gradually from 0 till PNP is opening?

LTSPICE file is attached.

Thanks.

Attachments

Last edited: