righteous

Full Member level 2

Gentlemen,

It is my objective to put as much current in the least amount of time possible through R5. However I'm experiencing rise and fall times of Q2 are anything but appropriate for a transistor like Q2, and due to my limited experience with analog design I'm finding it difficult to debug.

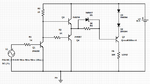

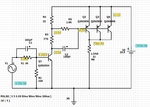

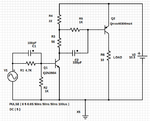

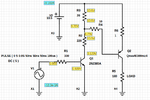

Here is my circuit, and DC calculations are courtesy of partsim.com:

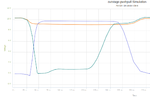

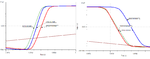

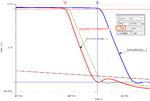

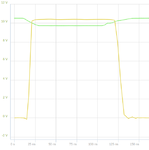

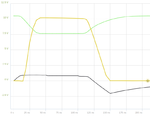

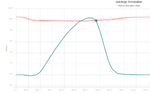

The V1 period is 100uS and pulse is 50ns rise, 50ns width, 50ns fall, Here is the simulated transient analysis where ORANGE is left side of R4, and RED is base of Q2, and BLUE is collector of Q2:

Any ideas/suggestion are highly welcome.

It is my objective to put as much current in the least amount of time possible through R5. However I'm experiencing rise and fall times of Q2 are anything but appropriate for a transistor like Q2, and due to my limited experience with analog design I'm finding it difficult to debug.

Here is my circuit, and DC calculations are courtesy of partsim.com:

The V1 period is 100uS and pulse is 50ns rise, 50ns width, 50ns fall, Here is the simulated transient analysis where ORANGE is left side of R4, and RED is base of Q2, and BLUE is collector of Q2:

Any ideas/suggestion are highly welcome.