d123

Advanced Member level 5

Hi,

Old circuit idea for ZCD, I wanted to see if it could actually be used in the real world (and how to go from sim-world AC generator version to a practical implementation). Would appreciate objective comments on circuit design mistakes, reasons why it couldn't work as desired, and/or things that would be glitchy. Thanks in advance if you have the patience and time.

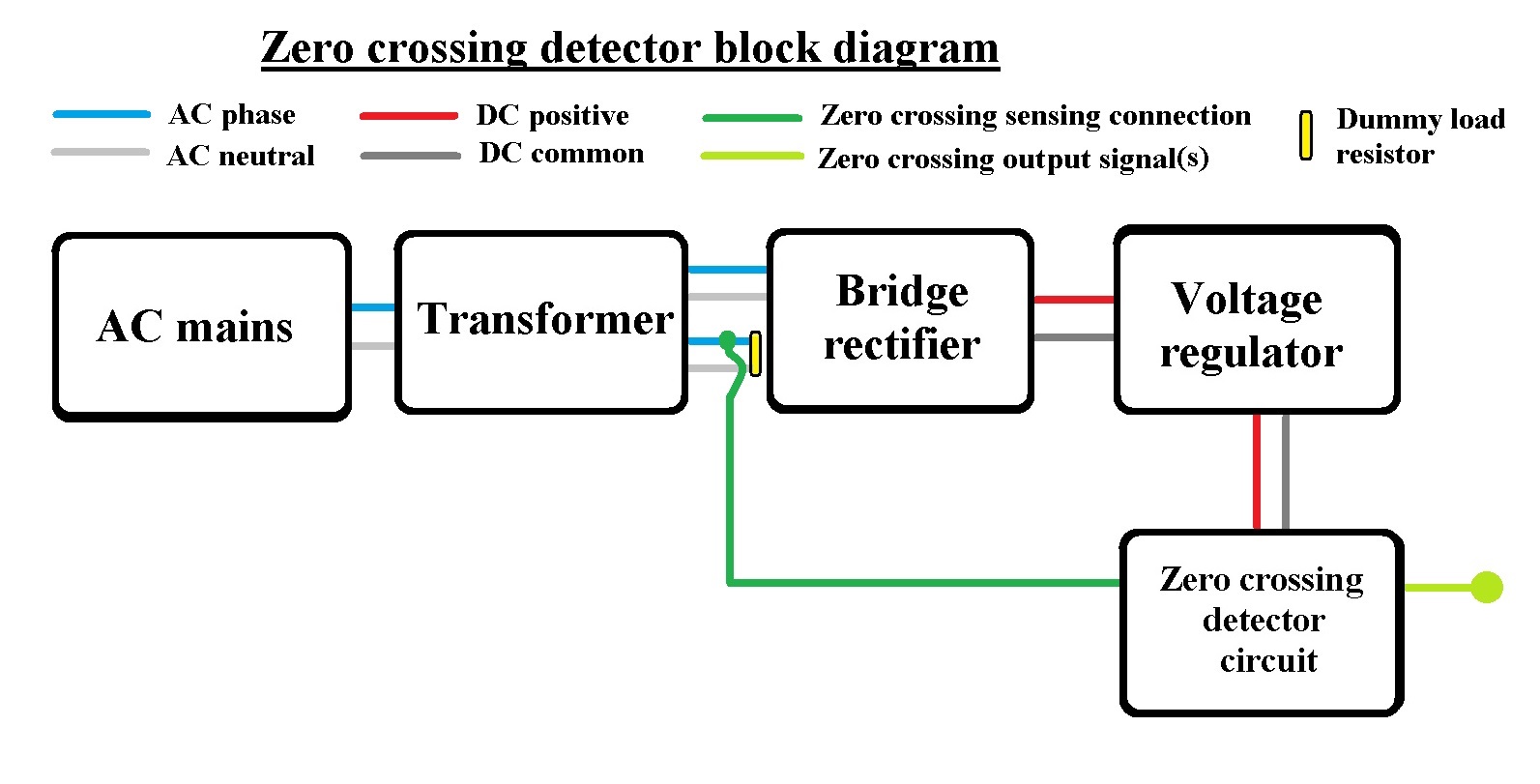

Block diagram:

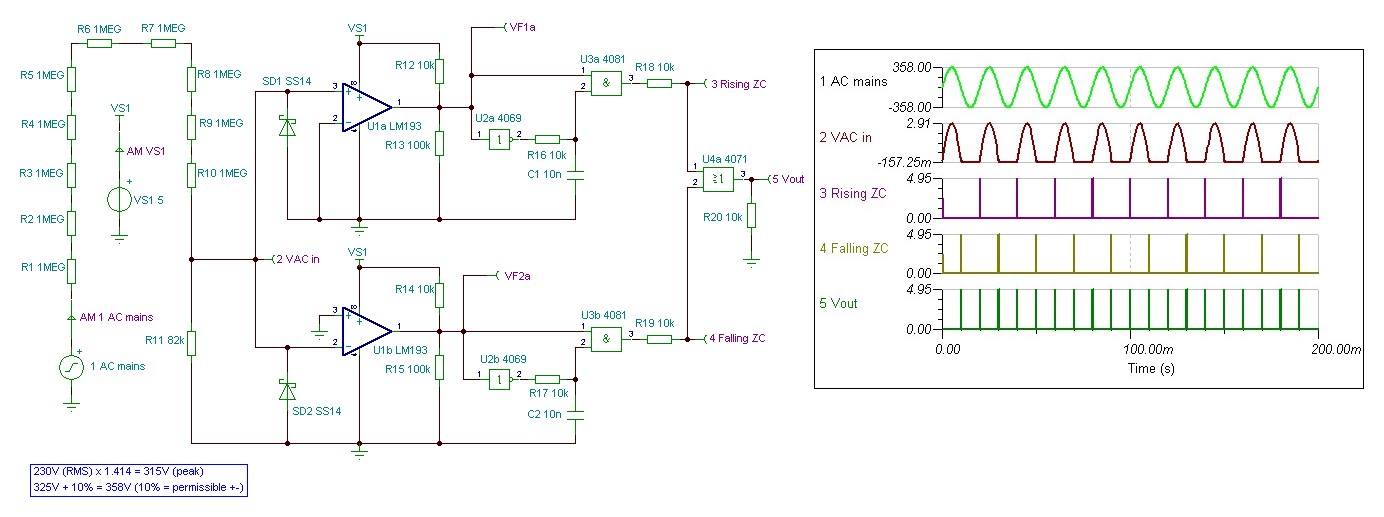

Original idea which has a transient result that (hopefully) shows the purpose of the circuit:

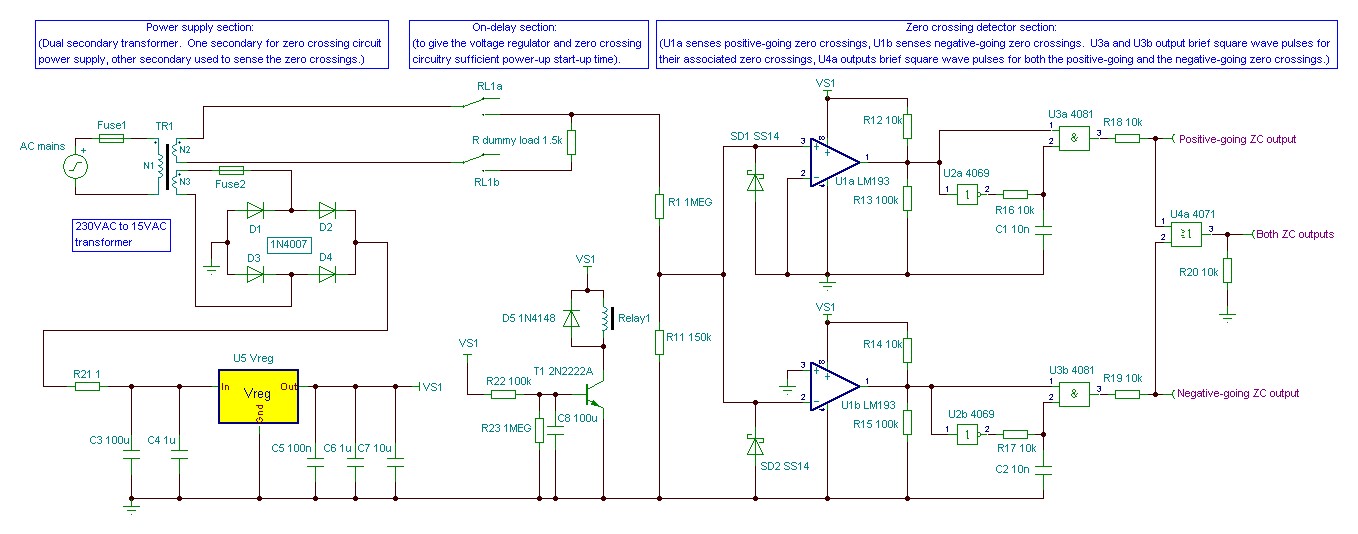

The version I think could work as a real circuit:

Reasons I can think of why it might not work as desired and/or can't/shouldn't be made:

1) I think I'm not allowed to plug a home-made transformer-based power supply into the AC mains unless it includes PFC, even for a circuit that would draw about 60mA.

2) Possibly, this circuit only works correctly (i.e. correctly meaning that the rising square wave pulse always occurs on positive-going and falling pulse always occurs on negative-going zero crossings) if the phase and neutral of the plug socket are known - if the wiring is reversed then the positive pulse would actually be the negative-going zero crossing and vice versa. Is that so?

3) I have read several things today that tell me that the secondary output of a transformer is either 180º out-of-phase with the primary AC sine wave, or that it is only a few degrees out of phase, or that it is never out-of-phase... Which of these is correct?

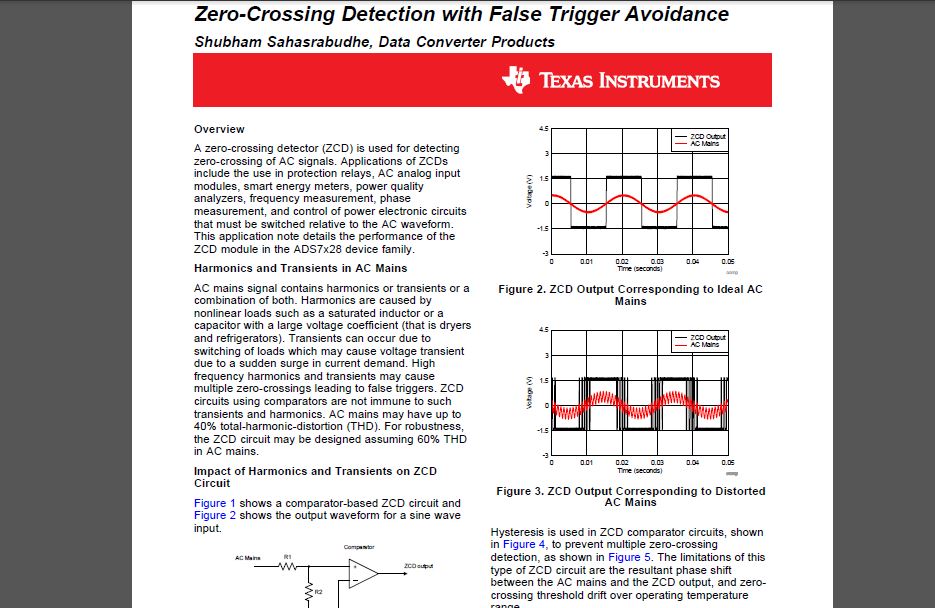

4) I see that chatter/false zero crossings is very possible from something I read. With regard to 'distorted AC mains', I have no idea how to implement comparator hysteresis for 0V references. Is that the same as for any other hysteresis? Is it really necessary? According to sbaa356, Zero-Crossing Detection with False Trigger Avoidance:

Thanks.

Old circuit idea for ZCD, I wanted to see if it could actually be used in the real world (and how to go from sim-world AC generator version to a practical implementation). Would appreciate objective comments on circuit design mistakes, reasons why it couldn't work as desired, and/or things that would be glitchy. Thanks in advance if you have the patience and time.

Block diagram:

Original idea which has a transient result that (hopefully) shows the purpose of the circuit:

The version I think could work as a real circuit:

Reasons I can think of why it might not work as desired and/or can't/shouldn't be made:

1) I think I'm not allowed to plug a home-made transformer-based power supply into the AC mains unless it includes PFC, even for a circuit that would draw about 60mA.

2) Possibly, this circuit only works correctly (i.e. correctly meaning that the rising square wave pulse always occurs on positive-going and falling pulse always occurs on negative-going zero crossings) if the phase and neutral of the plug socket are known - if the wiring is reversed then the positive pulse would actually be the negative-going zero crossing and vice versa. Is that so?

3) I have read several things today that tell me that the secondary output of a transformer is either 180º out-of-phase with the primary AC sine wave, or that it is only a few degrees out of phase, or that it is never out-of-phase... Which of these is correct?

4) I see that chatter/false zero crossings is very possible from something I read. With regard to 'distorted AC mains', I have no idea how to implement comparator hysteresis for 0V references. Is that the same as for any other hysteresis? Is it really necessary? According to sbaa356, Zero-Crossing Detection with False Trigger Avoidance:

Thanks.