weetabixharry

Full Member level 4

- Joined

- Oct 9, 2013

- Messages

- 232

- Helped

- 69

- Reputation

- 142

- Reaction score

- 73

- Trophy points

- 1,318

- Location

- Sweden

- Activity points

- 3,463

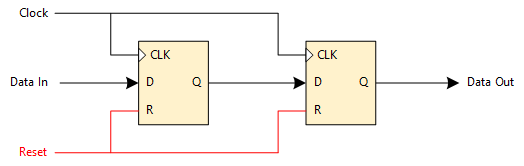

I am not aware of any reason why a 2 flip-flop (or N flip-flop) synchronizer should not have a reset. However, almost every implementation I have ever seen has no reset.

The only implementation I have found with a reset is the System Verilog implementation on p. 47 of this article.

- Is there some problem/drawback with resetting a 2 flip-flop synchronizer?

- Is the answer the same for both synchronous and asynchronous (i.e. asynchronous assert, synchronous de-assert) resets?

My Search Results:

These are the VHDL/Verilog implementations I have found and none of them have resets:- GitHub

- Lecture notes

- Online forums

The only implementation I have found with a reset is the System Verilog implementation on p. 47 of this article.