oberstet

Newbie level 6

Hi all,

as a RF newbie, I've been making some progress starting from EM modeling, having first PCBs designed and manufactured, but I am now stuck just before "closing the loop" with real-world measurements using LibreVNA =(

any help or hints would be greatly appreciated!

Cheers,

/Tobias

------

sorry if this all seems pretty basic, or even stupid or wrong: I am actually a SW engineer, and with RF and PCBs, I am really in a world very different from what I'm used to and new

anyways, my _plan_ for verifying my "modeling-to-realworld" workflow was the following:

1. model the PCB stack (2-Layer Teflon/PTFE) of the manufacturer (JLCPCB) I selected in openEMS - DONE!

2. use an impedance calculator for computing the PCB trace width for a single-ended 50R trace - DONE!

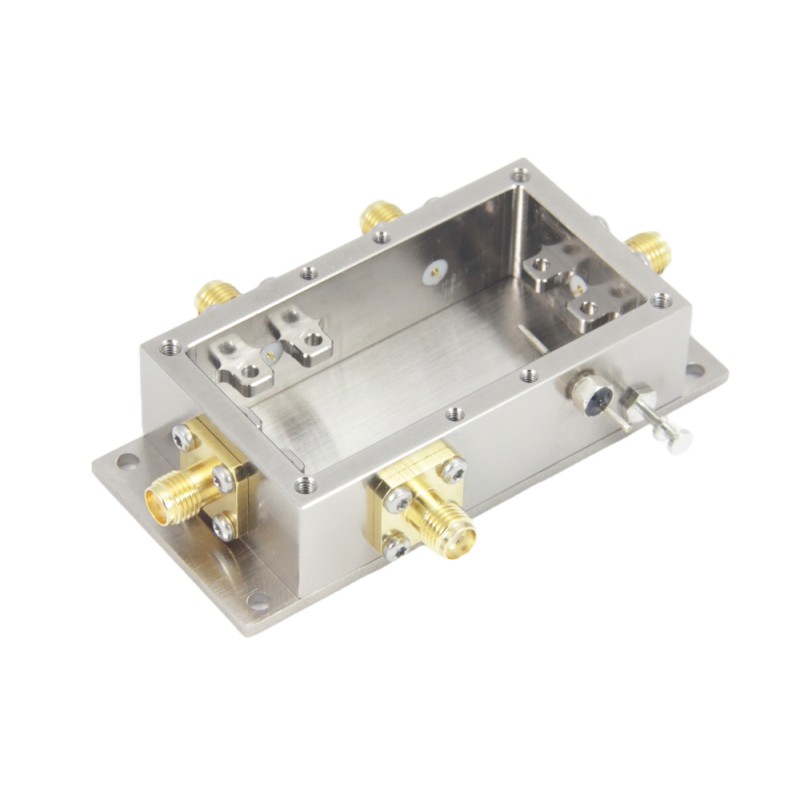

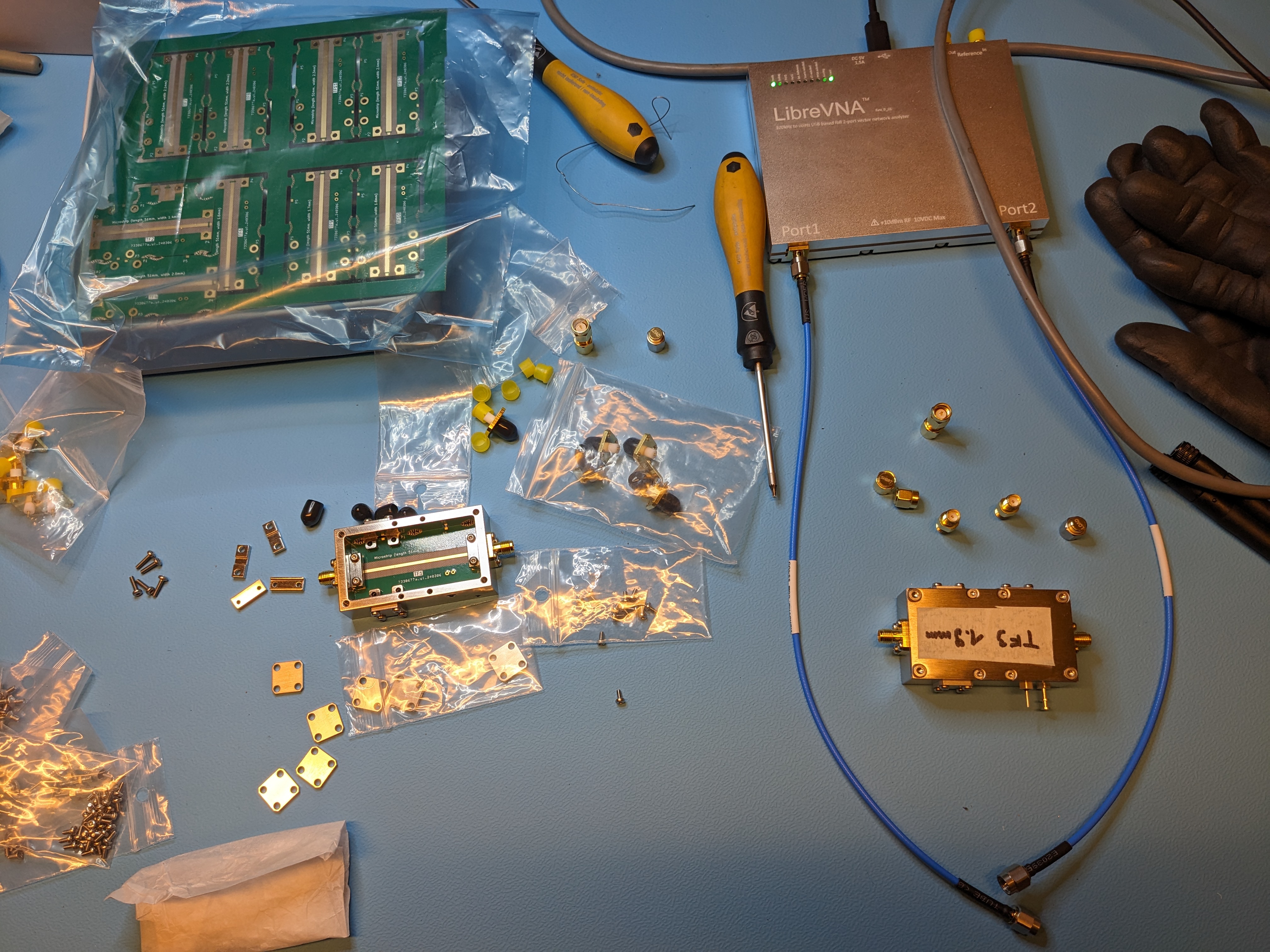

3. purchase LibreVNA and test fixture enclosures - DONE!

4. design a most simple PCB tile with a single 50R microstrip trace and with width 1.3mm - 2.4mm - DONE!

5. have those PCB tiles manufactured and mounted into the test fixtures - DONE!

6. calibrate LibreVNA using the included calkit and then measure S11 for PCB trace width 1.3mm and 1.9mm, and the calkit THRU - DONE!

pls see further below for screenshots.

my problem is: it "looks" good (that is, 1.9mm is actually "best" also in real world measurements), but I'm not sure!

also, at least rgd "phase", the results between CalKit-THRU and 1.9mm PCB trace look different. Is that because my PCB trace has 50+mm length (rather than "almost 0")?

the actual question I want to answer is:

Of all PCB trace widths I have (1.3-2.4mm), is 1.9mm indeed "the best" (rgd match to 50R)?

If so, that would mean: my modeling/simulation matches the real world (with PCB from my manufacturer and measuring using my VNA).

This would give me some reason for confidence that what I model and simulate in openEMS actually corresponds to the real world.

How do people usually do that? I mean: establish confidence in EM-model-to-real-world matching?

-----

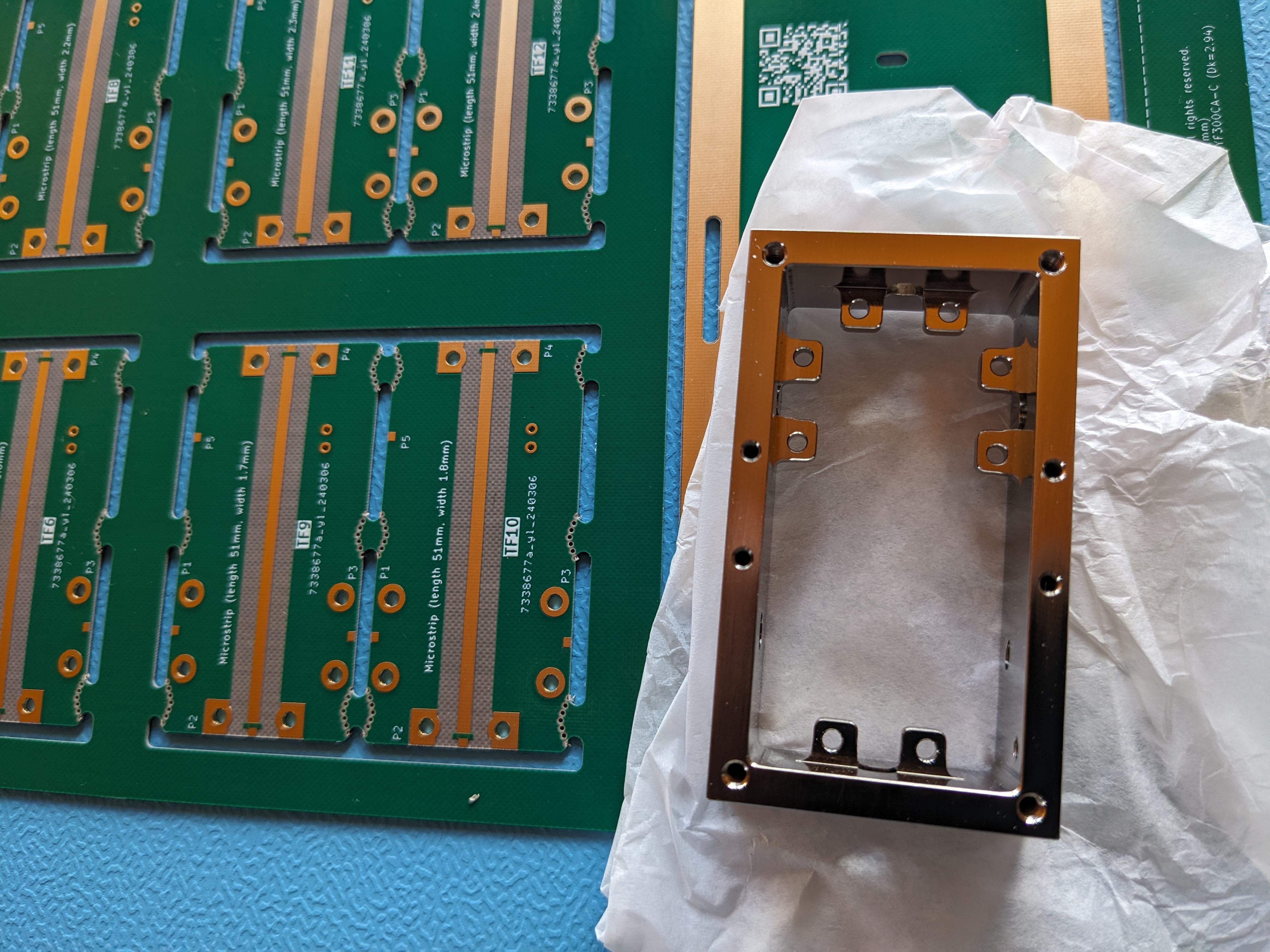

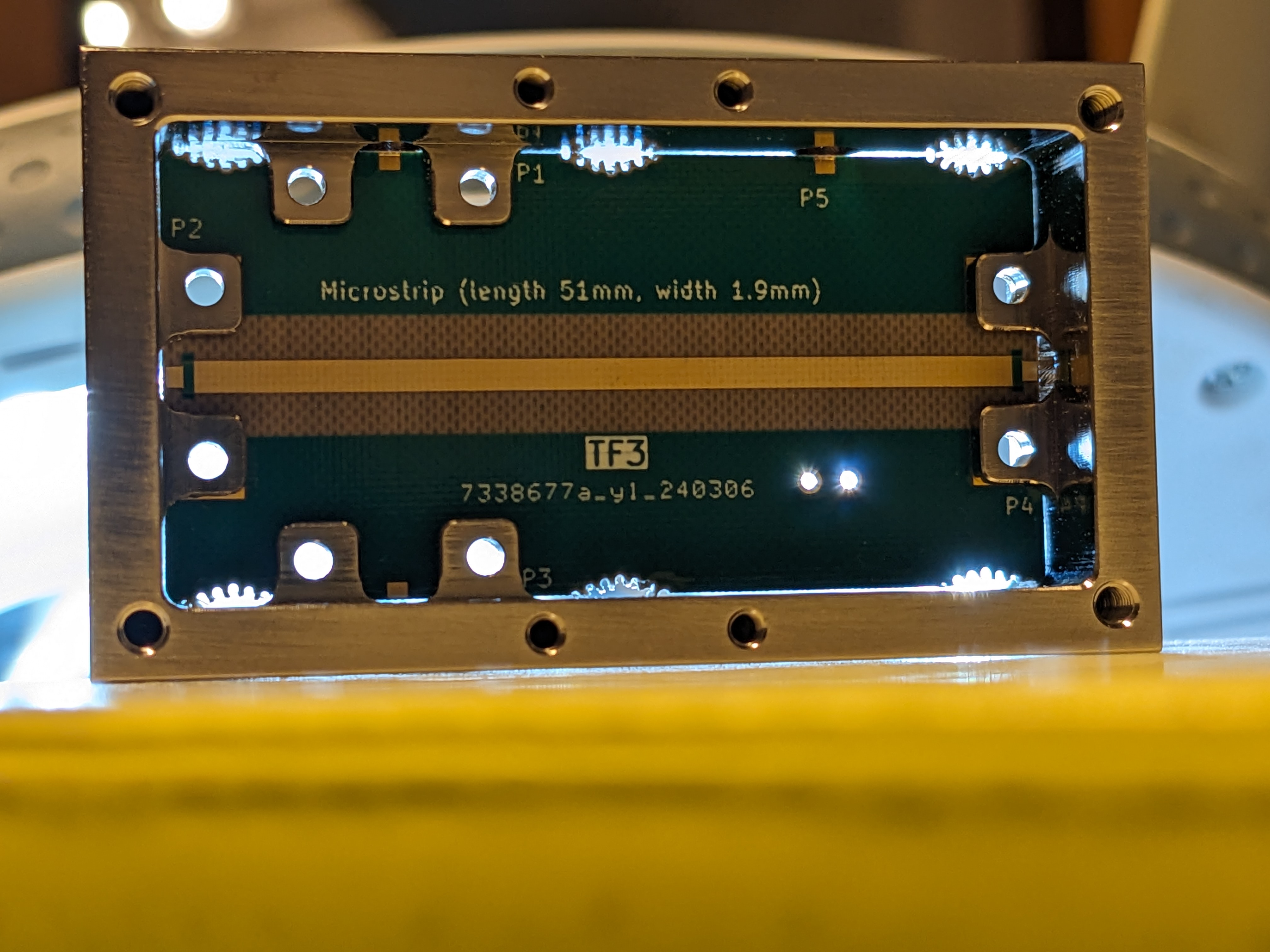

PCB trace tiles and test fixture:

-------------

LibreVNA / etc measurement setup:

-------------

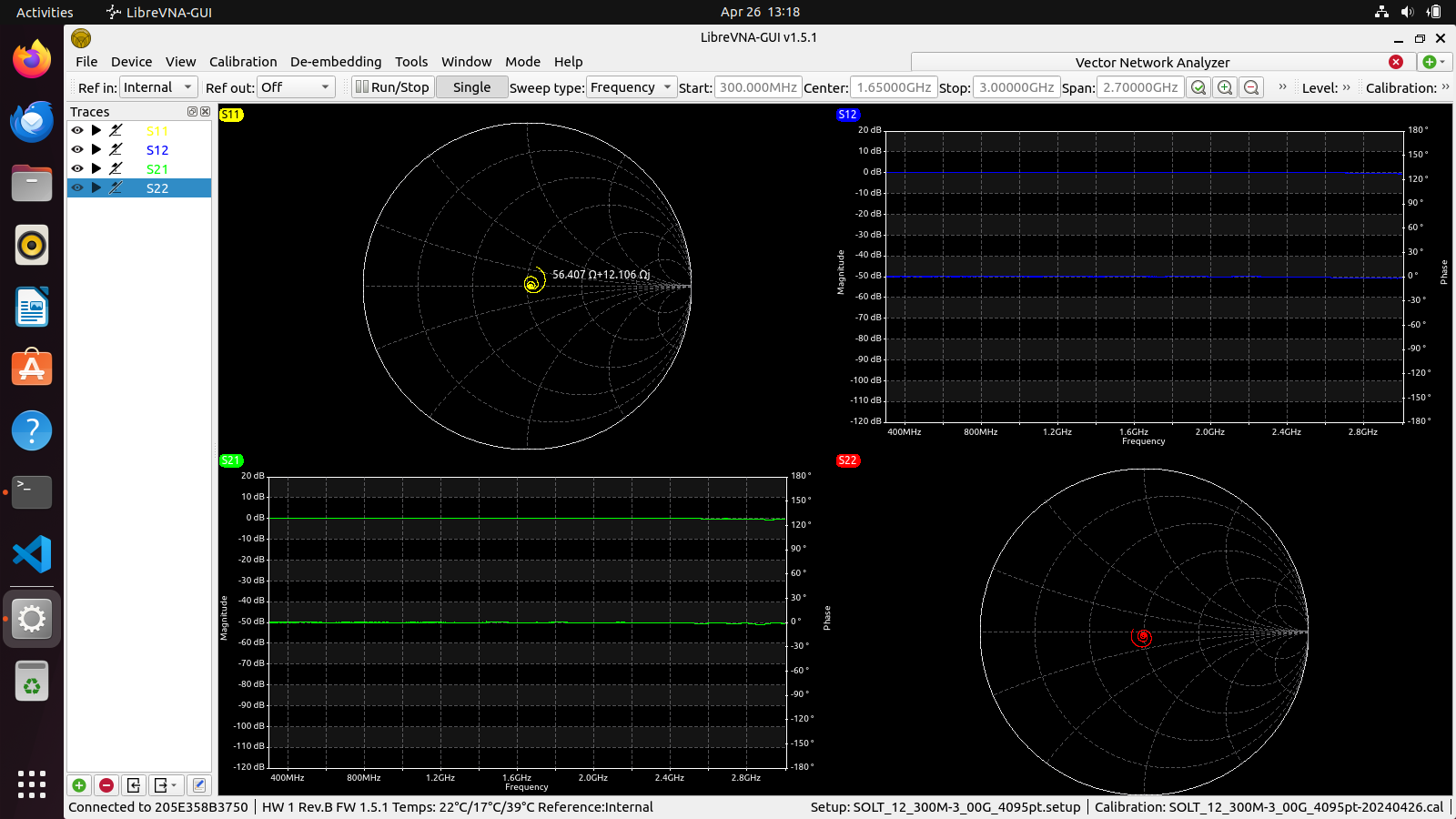

Results for LibreVNA Calkit THRU:

-------------

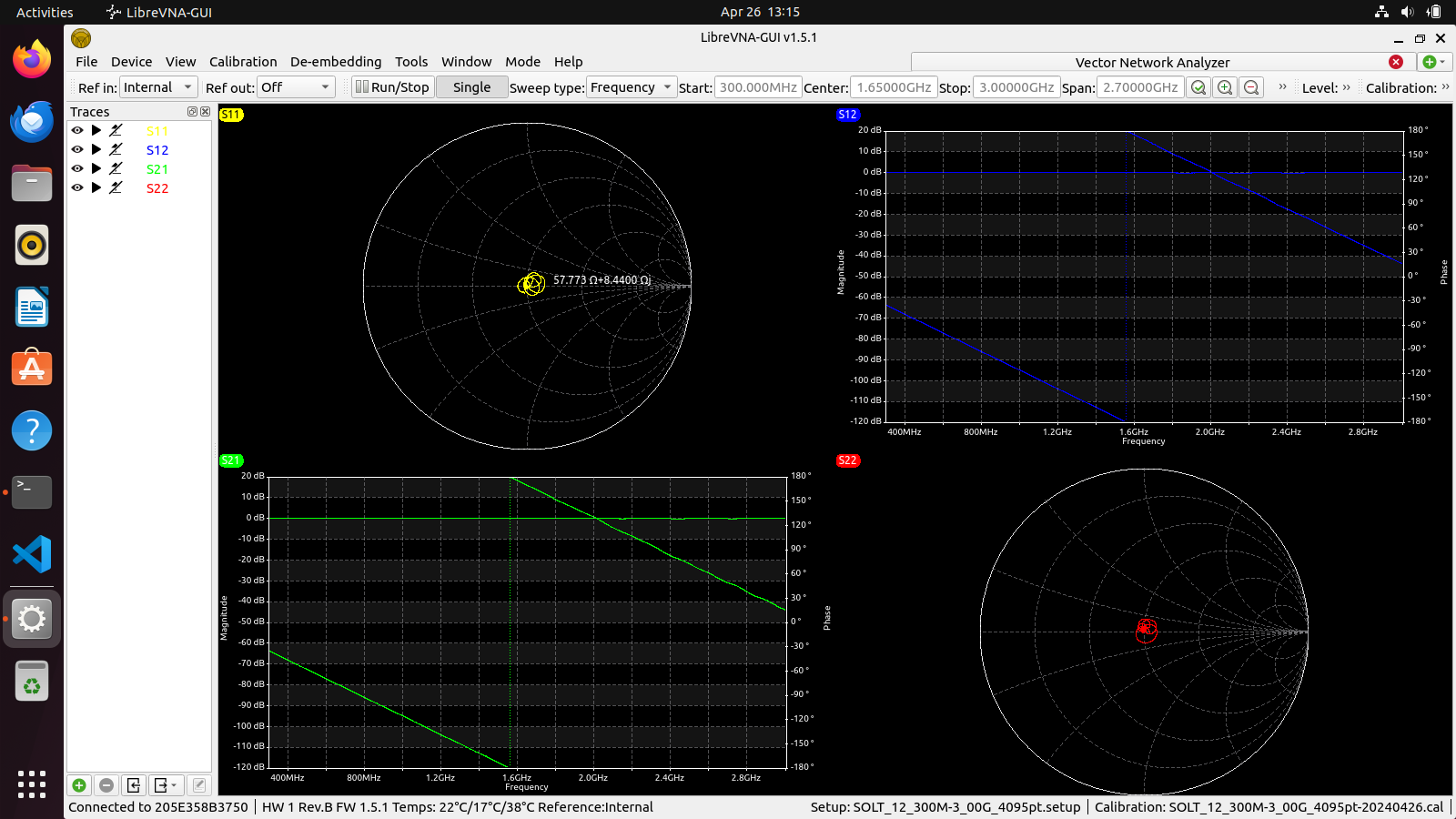

Results for my PCB trace in test fixture with width 1.9mm:

-------------

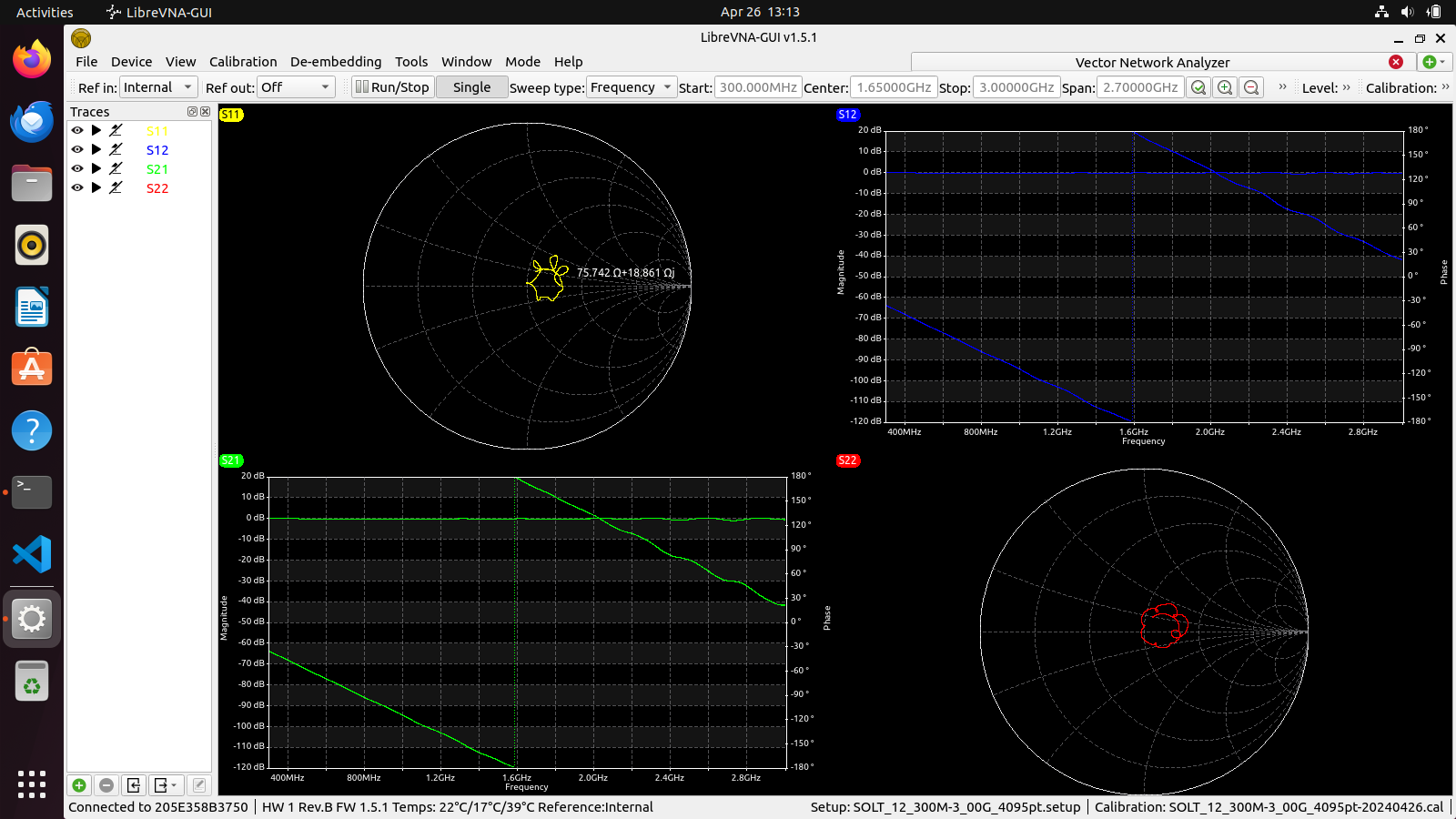

Results for my PCB trace in test fixture with width 1.3mm:

as a RF newbie, I've been making some progress starting from EM modeling, having first PCBs designed and manufactured, but I am now stuck just before "closing the loop" with real-world measurements using LibreVNA =(

any help or hints would be greatly appreciated!

Cheers,

/Tobias

------

sorry if this all seems pretty basic, or even stupid or wrong: I am actually a SW engineer, and with RF and PCBs, I am really in a world very different from what I'm used to and new

anyways, my _plan_ for verifying my "modeling-to-realworld" workflow was the following:

1. model the PCB stack (2-Layer Teflon/PTFE) of the manufacturer (JLCPCB) I selected in openEMS - DONE!

2. use an impedance calculator for computing the PCB trace width for a single-ended 50R trace - DONE!

3. purchase LibreVNA and test fixture enclosures - DONE!

4. design a most simple PCB tile with a single 50R microstrip trace and with width 1.3mm - 2.4mm - DONE!

5. have those PCB tiles manufactured and mounted into the test fixtures - DONE!

6. calibrate LibreVNA using the included calkit and then measure S11 for PCB trace width 1.3mm and 1.9mm, and the calkit THRU - DONE!

pls see further below for screenshots.

my problem is: it "looks" good (that is, 1.9mm is actually "best" also in real world measurements), but I'm not sure!

also, at least rgd "phase", the results between CalKit-THRU and 1.9mm PCB trace look different. Is that because my PCB trace has 50+mm length (rather than "almost 0")?

the actual question I want to answer is:

Of all PCB trace widths I have (1.3-2.4mm), is 1.9mm indeed "the best" (rgd match to 50R)?

If so, that would mean: my modeling/simulation matches the real world (with PCB from my manufacturer and measuring using my VNA).

This would give me some reason for confidence that what I model and simulate in openEMS actually corresponds to the real world.

How do people usually do that? I mean: establish confidence in EM-model-to-real-world matching?

-----

PCB trace tiles and test fixture:

-------------

LibreVNA / etc measurement setup:

-------------

Results for LibreVNA Calkit THRU:

-------------

Results for my PCB trace in test fixture with width 1.9mm:

-------------

Results for my PCB trace in test fixture with width 1.3mm: