Junus2012

Advanced Member level 5

Dear frank,

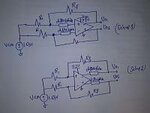

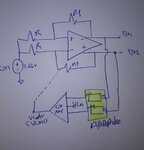

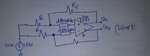

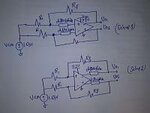

in the pdf Idaho he changed the place of the difstbprobe when he was simulating the CMFB loop however he was using cmdmprobe as I am again reffereing to it below.

But I would also get confirmed about your suggestion more clearly, according to you that the same circuit configuration used to simulate the differential mode properties using the diffstbstbprobe will be exactly the same to be used for simulating the common mode CMFB loop proparties but by only changing the STB setting from the simulator from differential to common,

the setup I am again bringing it near to you here

in the pdf Idaho he changed the place of the difstbprobe when he was simulating the CMFB loop however he was using cmdmprobe as I am again reffereing to it below.

But I would also get confirmed about your suggestion more clearly, according to you that the same circuit configuration used to simulate the differential mode properties using the diffstbstbprobe will be exactly the same to be used for simulating the common mode CMFB loop proparties but by only changing the STB setting from the simulator from differential to common,

the setup I am again bringing it near to you here