PorDeseign00

Junior Member level 1

Hello everyone.

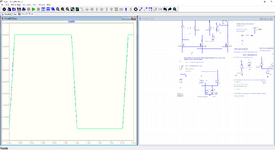

I have a problem with the simulation of the slew rate of a two-stage op amp on Ltspice..

When I configure the op amp as a unity gain buffer the simulation goes into an infinite loop and I can't see the response speed of my op amp. when I connect the square wave pulse to one input terminal Vin+ of the op amp and connect the other to gnd without carrying out the feedback, I can measure the slew rate, but I don't think it's the right method.

Thank you so much!!

I have a problem with the simulation of the slew rate of a two-stage op amp on Ltspice..

When I configure the op amp as a unity gain buffer the simulation goes into an infinite loop and I can't see the response speed of my op amp. when I connect the square wave pulse to one input terminal Vin+ of the op amp and connect the other to gnd without carrying out the feedback, I can measure the slew rate, but I don't think it's the right method.

Thank you so much!!