pifouille

Junior Member level 1

Hi,

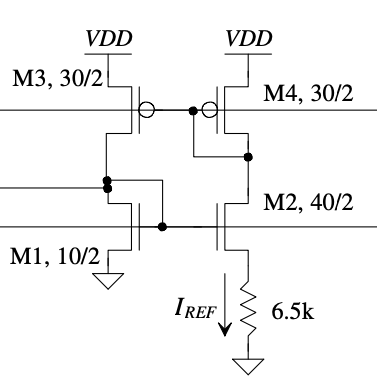

I am simulating in LTSpice the self-biased reference shown below without any startup circuit.

This is fig. 20.15 of J. Baker 4th ed.

I used L=2u for all transistors with W/L as shown on the figure.

Models are N_1u and P_1u from cmosedu.com

I was wondering wether a start-up circuit is really necessary here if the P current mirror

sets a current ratio different from 1. So I first simulated the circuit as it is and without any start-up

hoping it would settle to a zero-current state with Vg,n=0 and Vg,p=Vdd.

However, I can't manage to get the circuit to settle this 0-current OP by simulation

-- A transient simulation with Vdd going from 0 to 10 gets to the 20uA OP (which is the other equilibrium for this circuit)

-- a DC simulation on the same range leads to the same results, even with a .IC or .NODESET statement

-- A .OP simulaltion with a .NODESET statement for the gate voltages leads again to the same results.

I was wondering if anybody could help

Thanks in advance

I am simulating in LTSpice the self-biased reference shown below without any startup circuit.

This is fig. 20.15 of J. Baker 4th ed.

I used L=2u for all transistors with W/L as shown on the figure.

Models are N_1u and P_1u from cmosedu.com

I was wondering wether a start-up circuit is really necessary here if the P current mirror

sets a current ratio different from 1. So I first simulated the circuit as it is and without any start-up

hoping it would settle to a zero-current state with Vg,n=0 and Vg,p=Vdd.

However, I can't manage to get the circuit to settle this 0-current OP by simulation

-- A transient simulation with Vdd going from 0 to 10 gets to the 20uA OP (which is the other equilibrium for this circuit)

-- a DC simulation on the same range leads to the same results, even with a .IC or .NODESET statement

-- A .OP simulaltion with a .NODESET statement for the gate voltages leads again to the same results.

I was wondering if anybody could help

Thanks in advance