deardeepa76

Junior Member level 3

- Joined

- Dec 8, 2011

- Messages

- 29

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,491

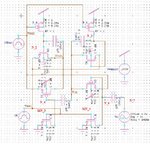

This is the schematic for the circuit. I have changed the typo error, but still I am not getting proper result.

This is the schematic for the circuit. I have changed the typo error, but still I am not getting proper result.

Code:

* ULV Inverting current mirror recharge freq 25MHz

********* Simulation Settings - General section *********

.include "D:\HSPICE\NewCSFGBkup\t96w_9sf_9m_lb_3-params.txt"

.param vdd=450m v0='vdd/3.6' va='vdd/3.6' freq=8MEG delay=0 theta=0 phase=0

********* Simulation Settings - Parameters and SPICE Options *********

*-------- Devices: SPICE.ORDER > 0 --------

CCinn1 Vin N_3 .0002p

CCinn2 Vin N_4 1p

CCinp1 N_7 N_6 1p

CCinp2 Vout N_2 .0002p

MN_3 N_4 Vdd1 Gnd Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MN_4 N_6 Vdd1 Gnd Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MQ1 Vin N_3 Vdd1 Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MQ4 Vout N_2 Vdd1 Gnd CMOSN W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MQ2 Vout N_4 Vdd2 Vdd CMOSP W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MQ3 Vin N_6 Vdd2 Vdd CMOSP W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MP_1 N_2 Vdd2 Vdd Vdd CMOSP W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

MP_2 N_3 Vdd2 Vdd Vdd CMOSP W=2.5u L=250n AS=2.25p PS=6.8u AD=2.25p PD=6.8u

VVsupply Vdd Gnd DC vdd

VVf Vdd1 Gnd PULSE(0 vdd 0 2.5n 2.5n 15n 40n)

VVfbar Vdd2 Gnd PULSE(0 vdd 20n 2.5n 2.5n 15n 40n)

VVa N_7 Gnd SIN(v0 va freq delay theta phase) $sinusoidal sweep

********* Simulation Settings - Analysis section *********

.tran 40n 1u

.print tran ID(MQ1)

.print tran ID(MQ2)

.meas maxIn MAX I(MQ1) from=900ns to=997ns

.meas maxIout MAX I(MQ2) from=900ns to=997ns

********* Simulation Settings - Additional SPICE commands *********

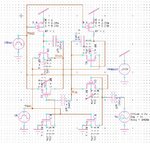

.endBut when I keep all capacitors as 1pF and keep clock pulse height as 1V I am getting this output