seridj_mse

Member level 2

- Joined

- Jan 18, 2021

- Messages

- 53

- Helped

- 0

- Reputation

- 0

- Reaction score

- 2

- Trophy points

- 8

- Activity points

- 311

HI,

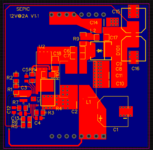

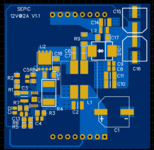

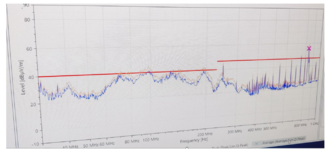

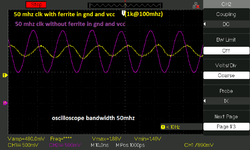

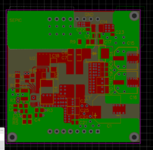

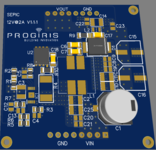

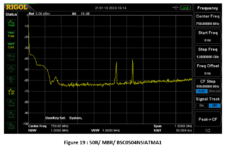

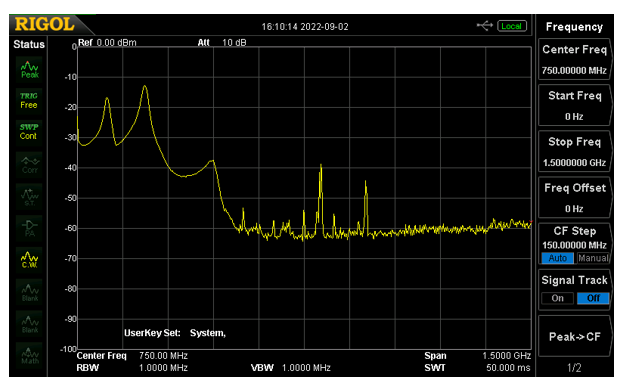

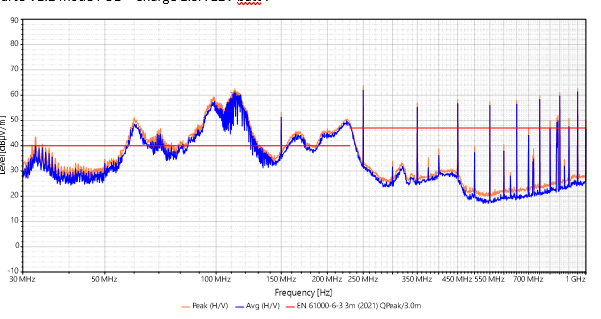

We have tested our equipment SEPIC DC DC input:9-30V output : 12V/24W (PCB 2LAYER) for CISPR 16 radiated emission limits. The emission result is attached. I have trouble shooted the problem element.

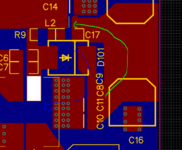

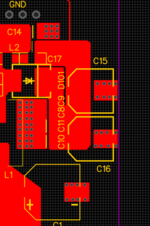

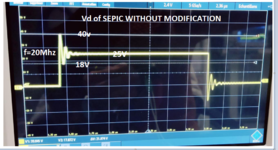

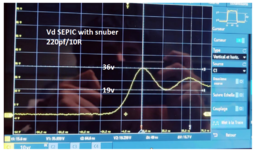

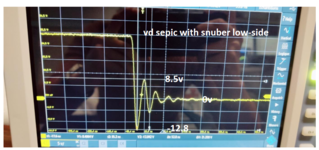

for pics i know its about quartz 50Mhz but the probleme is with renonant , i tried with RC , and RDC snubber but i cant solve probleme

We have tested our equipment SEPIC DC DC input:9-30V output : 12V/24W (PCB 2LAYER) for CISPR 16 radiated emission limits. The emission result is attached. I have trouble shooted the problem element.

for pics i know its about quartz 50Mhz but the probleme is with renonant , i tried with RC , and RDC snubber but i cant solve probleme