LvW

Advanced Member level 6

- Joined

- May 7, 2008

- Messages

- 5,923

- Helped

- 1,754

- Reputation

- 3,514

- Reaction score

- 1,369

- Trophy points

- 1,393

- Location

- Germany

- Activity points

- 40,624

Hi palmeiras,

I`ll try to answer your questions:

1) I cannot see how breaking the loop in this conditions (small output resistance + large input resistance), will mitigate the impact of breaking the loop, in terms of impedance. Do you have a suggestion for me to understand this rule?

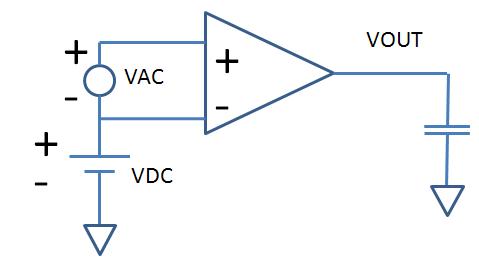

This rule (low output resistance) is important only if you choose the "simple" way of simulating the loop gain (that means: without mirroring the load). Example: 1kohm output resistance is connected to a 1kohm load. Result: output voltage is different with/without load. If you break the loop at this point there is no current anymore flowing out of the output node, unless you connect a "mirror load" at this point. In most cases, however,this load is unknown and frequency dependent. Then, an exact mirror is not possible. If the output resitance is pretty low and/or the connected load (input of the next stage) is sufficient high you don`t need such a mirror - and the error is (hopefully) negligible.

2) You commented about circuits with amp. op. It is normal to break the loop at the output node. However, amplifiers often have high output resistance in order to increase the small signal gain. Am I correct or not?.

Really "often" ? What I call "operational amplifier" is a voltage amplifier with a high input and a low output resistance.

Of course, if this is not fulfilled, my arguments are not valid anymore.

For example, differential pair with cascade devices or a folded cascade amplifier, present transistors with high values of output resistance. When in these cases, the amp. op output resistance is high, why is it proper to break the loop there?

I think that such amplifiers with a current output are called OTA or transconductor or voltage-current transducer.

In such a case, most probably, the high resistance voltage input is the best point for breaking the loop. Or you must apply more sophisticated arrangements that are independent on such restrictions (Middlebrook,...)

3) When we are breaking a loop at some node, we always are changing the load conditions there. Am I correct or not?

So, the key point on your explanation is that "we should minimize the change of the impedance as much as we can". Did I get your message?

Yes, correct. Remember: Nothing in electronics is correct by 100%. Even each multimeter application changes the value to be measured.

Regards

LvW

I`ll try to answer your questions:

1) I cannot see how breaking the loop in this conditions (small output resistance + large input resistance), will mitigate the impact of breaking the loop, in terms of impedance. Do you have a suggestion for me to understand this rule?

This rule (low output resistance) is important only if you choose the "simple" way of simulating the loop gain (that means: without mirroring the load). Example: 1kohm output resistance is connected to a 1kohm load. Result: output voltage is different with/without load. If you break the loop at this point there is no current anymore flowing out of the output node, unless you connect a "mirror load" at this point. In most cases, however,this load is unknown and frequency dependent. Then, an exact mirror is not possible. If the output resitance is pretty low and/or the connected load (input of the next stage) is sufficient high you don`t need such a mirror - and the error is (hopefully) negligible.

2) You commented about circuits with amp. op. It is normal to break the loop at the output node. However, amplifiers often have high output resistance in order to increase the small signal gain. Am I correct or not?.

Really "often" ? What I call "operational amplifier" is a voltage amplifier with a high input and a low output resistance.

Of course, if this is not fulfilled, my arguments are not valid anymore.

For example, differential pair with cascade devices or a folded cascade amplifier, present transistors with high values of output resistance. When in these cases, the amp. op output resistance is high, why is it proper to break the loop there?

I think that such amplifiers with a current output are called OTA or transconductor or voltage-current transducer.

In such a case, most probably, the high resistance voltage input is the best point for breaking the loop. Or you must apply more sophisticated arrangements that are independent on such restrictions (Middlebrook,...)

3) When we are breaking a loop at some node, we always are changing the load conditions there. Am I correct or not?

So, the key point on your explanation is that "we should minimize the change of the impedance as much as we can". Did I get your message?

Yes, correct. Remember: Nothing in electronics is correct by 100%. Even each multimeter application changes the value to be measured.

Regards

LvW