Persian_Men

Junior Member level 1

- Joined

- Nov 29, 2008

- Messages

- 18

- Helped

- 5

- Reputation

- 10

- Reaction score

- 4

- Trophy points

- 1,283

- Activity points

- 1,455

Dominik Przyborowski say:

how i can calculate r2r ladder network resistor value?

thanks

output port value increased step by step in this loop to build a ramp signal,r2r ladder convert this fragment value to analog signal,ODR is register to write GPIO port value,frequency can be increased by increase jump step in base loop.

similar technique like NCO oscillators.my osc is frequency BW is 20MHz,Micro AZ.

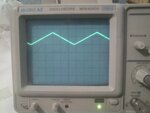

thank,yes of course ,i have a big problem in high freq>50Khz,please help me to reduced this problem or show me how replace this circuit with other circuit.please recommend new circuit schematic for build dac circuit.Use smaller resistors and external low resistance switches driving from uC.

how i can calculate r2r ladder network resistor value?

Can you explain what your code is doing ? GPIO -> ODR=x ?? And how do you set the update rate in your loop for specific frequencies ?

In addition, what is your oscilloscope specs ? I cannot make out which make/ model it is.

thanks

output port value increased step by step in this loop to build a ramp signal,r2r ladder convert this fragment value to analog signal,ODR is register to write GPIO port value,frequency can be increased by increase jump step in base loop.

similar technique like NCO oscillators.my osc is frequency BW is 20MHz,Micro AZ.