Persian_Men

Junior Member level 1

Hi guys.

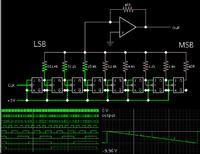

i design r-2r ladder dac semilar this schematic for design signal generator.

i use ARM GPIO port to connect to r-2r dac.

i design 10bit r-2r ladder network.

when i want to build ramp signal output is not equal ramp signal

ramp code is:

when i was use 8bit resolution i see a complate ramp signal:

anybody can help me?

i design r-2r ladder dac semilar this schematic for design signal generator.

i use ARM GPIO port to connect to r-2r dac.

i design 10bit r-2r ladder network.

when i want to build ramp signal output is not equal ramp signal

ramp code is:

Code C - [expand]

when i was use 8bit resolution i see a complate ramp signal:

anybody can help me?