problem simulation delay line

- Thread starter yefj

- Start date

D.A.(Tony)Stewart

Advanced Member level 7

- Joined

- Sep 26, 2007

- Messages

- 10,294

- Helped

- 1,867

- Reputation

- 3,739

- Reaction score

- 2,515

- Trophy points

- 1,413

- Location

- Richmond Hill, ON, Canada

- Activity points

- 64,857

If your model satisfies the specs, it's a good model.

If you don't have Design specs, you don't have a design that can be validated.

If you don't have Design specs, you don't have a design that can be validated.

- Joined

- Jan 22, 2008

- Messages

- 53,695

- Helped

- 14,811

- Reputation

- 29,919

- Reaction score

- 14,437

- Trophy points

- 1,393

- Location

- Bochum, Germany

- Activity points

- 303,571

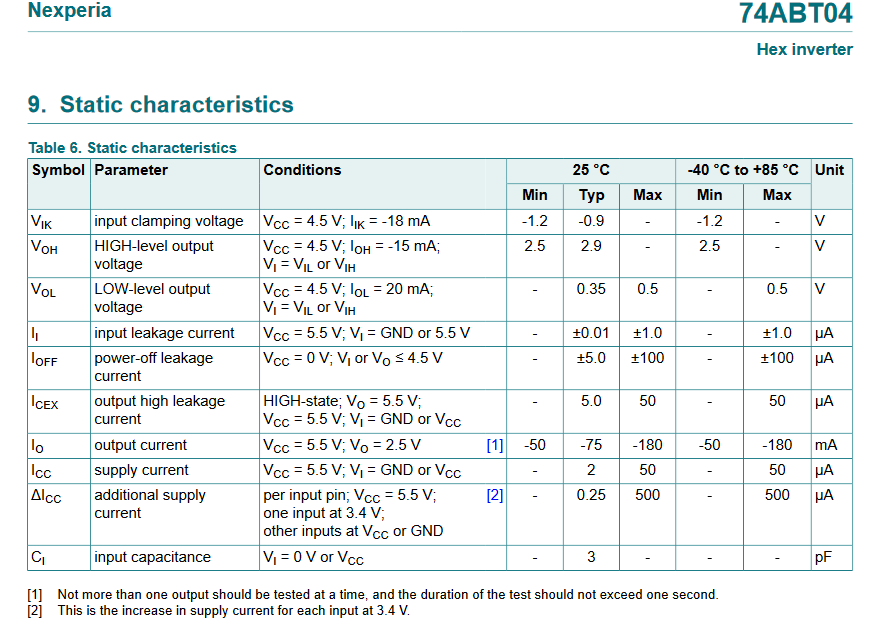

NXP used to have 74ABT SPICE models, see e.g. https://groups.io/g/LTspice/topic/simulating_74abt04_hex/105363417

SPICE model can be expected to represent nonlinear CMOS driver characteristic quite exactly, in most cases an equivalent linear driver impedance should give acceptable results.

SPICE model can be expected to represent nonlinear CMOS driver characteristic quite exactly, in most cases an equivalent linear driver impedance should give acceptable results.

D.A.(Tony)Stewart

Advanced Member level 7

- Joined

- Sep 26, 2007

- Messages

- 10,294

- Helped

- 1,867

- Reputation

- 3,739

- Reaction score

- 2,515

- Trophy points

- 1,413

- Location

- Richmond Hill, ON, Canada

- Activity points

- 64,857

The advanced Spice models not only adds the FET parameters but also adds the package ESL (nH) and parasitic pF for every lead.

If you simulate as in the datasheet with 250 Ohms 50 pF to 2.5V and get the same min, typ and max delay time by changing the Rs fixed value, then you are pretty close to testing the room temp model of 25'C with 50 pF fix load. But this requires unequal Zoh and Zol from the static Parameters. ABT types are different from HC and ALC and the dozen other CMOS families.

Variations in Vdd and Tamb. have more effects not included in the models.

I doubt 74ABT is your ideal choice even with no design specs.

If you simulate as in the datasheet with 250 Ohms 50 pF to 2.5V and get the same min, typ and max delay time by changing the Rs fixed value, then you are pretty close to testing the room temp model of 25'C with 50 pF fix load. But this requires unequal Zoh and Zol from the static Parameters. ABT types are different from HC and ALC and the dozen other CMOS families.

Variations in Vdd and Tamb. have more effects not included in the models.

I doubt 74ABT is your ideal choice even with no design specs.

Last edited:

- Joined

- Apr 1, 2011

- Messages

- 15,820

- Helped

- 2,918

- Reputation

- 5,850

- Reaction score

- 3,075

- Trophy points

- 1,393

- Location

- Minneapolis, Minnesota, USA

- Activity points

- 118,468

I'm looking at the schematic in post #40. The LC delay ladder. No matter how carefully you craft the applied pulse wave, it gets distorted as it carries through the ladder network. Its rectangular appearance is barely recognizable by the time it reaches the output.

The LC ladder imposes its own rise and fall times. This is easy to observe in animated simulation. You can build the circuit in hardware but in fact the animated simulation (Falstad's) is so fascinating to watch that it's more interesting than a hardware version. Electrons (or current bundles) go round the LC loops one after the next, and back-and-forth from loop to loop.

A thread here once brought up an old-style musical instrument phasor box that contained several coils of a size that surely had to add lots of bulk. I'm sure it worked to some degree but the potential behind phasing had to wait for digital methods to make it practical. Even a tape delay machine had its bulk and expense.

The LC ladder imposes its own rise and fall times. This is easy to observe in animated simulation. You can build the circuit in hardware but in fact the animated simulation (Falstad's) is so fascinating to watch that it's more interesting than a hardware version. Electrons (or current bundles) go round the LC loops one after the next, and back-and-forth from loop to loop.

A thread here once brought up an old-style musical instrument phasor box that contained several coils of a size that surely had to add lots of bulk. I'm sure it worked to some degree but the potential behind phasing had to wait for digital methods to make it practical. Even a tape delay machine had its bulk and expense.

D.A.(Tony)Stewart

Advanced Member level 7

- Joined

- Sep 26, 2007

- Messages

- 10,294

- Helped

- 1,867

- Reputation

- 3,739

- Reaction score

- 2,515

- Trophy points

- 1,413

- Location

- Richmond Hill, ON, Canada

- Activity points

- 64,857

Even with mismatched impedance I can improve the (load) signal conditioner, using carefully selected components such as very low pF transistors < 3.3pF and Schottky diodes you can condition the 1st pulse and try to suppress the reflections. The higher Q realizes gain in voltage and slew rate , then buffered and clamped by BAT56 diodes to logic supply rails. Using substitutions like PN2222 and 1N5717 makes it substantially worse. Low DCR Inductors can make it worse and more damping load reduces slew rate.

This is reminiscent of early posts on duplicate questions to use a ladder filter instead of a Gaussian Filter, which seems to have been ignored.

CML or PECL logic would perform far better than this comment, as mentioned in the past.

This comment is not intended to be an ideal design, but just what you can do in the lab to explore or use known tricks to simulate better signal conditioning.

But as I have been saying, until you define realistic design specs with a purpose for all I/O parameters {delay, V, I, Z,f, ambient} with tolerances, you are just learning the slow, hard way.

Changes:

Moved C3 to end of ladder filter as it was theoretically useless on a 0 ohm Voltage pulse source.

Add a simple bipolar Emitter Follower and BAT54 diode clamps to 3.3V, 0V.

Schematic clean-up and added .net test points for plot labels.

Increased PWL to 235 ns with 0 delay to match filter.

Added Rs to ideal pulse gen.

Non-Ideal characteristics:

Asymmetric delays Tr, Tf, non-uniform spectral group delay, thus delays depend slightly with input pulse width which changes spectrum where group delay changes

Delay is dependent on 1ns input rise time, then increases with input.

Time-domain Reflections still exist from impedance mismatch.

I think there is a better way to show plots with PW50% pulse width and markers to show tPLH and tPHL in LTSpice, (rather than just the floating curser... Anyone?

Feel free to play around with above simulation , until real design specs are forthcoming.

This is reminiscent of early posts on duplicate questions to use a ladder filter instead of a Gaussian Filter, which seems to have been ignored.

CML or PECL logic would perform far better than this comment, as mentioned in the past.

This comment is not intended to be an ideal design, but just what you can do in the lab to explore or use known tricks to simulate better signal conditioning.

But as I have been saying, until you define realistic design specs with a purpose for all I/O parameters {delay, V, I, Z,f, ambient} with tolerances, you are just learning the slow, hard way.

Changes:

Moved C3 to end of ladder filter as it was theoretically useless on a 0 ohm Voltage pulse source.

Add a simple bipolar Emitter Follower and BAT54 diode clamps to 3.3V, 0V.

Schematic clean-up and added .net test points for plot labels.

Increased PWL to 235 ns with 0 delay to match filter.

Added Rs to ideal pulse gen.

Non-Ideal characteristics:

Asymmetric delays Tr, Tf, non-uniform spectral group delay, thus delays depend slightly with input pulse width which changes spectrum where group delay changes

Delay is dependent on 1ns input rise time, then increases with input.

Time-domain Reflections still exist from impedance mismatch.

I think there is a better way to show plots with PW50% pulse width and markers to show tPLH and tPHL in LTSpice, (rather than just the floating curser... Anyone?

Feel free to play around with above simulation , until real design specs are forthcoming.

Attachments

Last edited:

D.A.(Tony)Stewart

Advanced Member level 7

- Joined

- Sep 26, 2007

- Messages

- 10,294

- Helped

- 1,867

- Reputation

- 3,739

- Reaction score

- 2,515

- Trophy points

- 1,413

- Location

- Richmond Hill, ON, Canada

- Activity points

- 64,857

Since time delay is a derivative of phase shift (d phi/df), then SNR is most important to your design spec to limit phase noise and tolerance on variances that result in jitter from Signal BW, Noise BW, nonlinearity, comparator or "slicer" & Vref variances, prop delay, impedance mismatch reflections & changes in ambient conditions to components and supply V. SNR is deterministic to errors.

Do the math and define what you need, before your next attempt.

Do the math and define what you need, before your next attempt.

Similar threads

-

-

Problem delay in switching current steering differential DAC

- Started by PhdSA

- Replies: 5

-

transistor limiting current on the output load problem in simulation

- Started by yefj

- Replies: 1

-

-

Driving different loads but need same delay and same slew rate

- Started by electronics_eel

- Replies: 3