Rajinder1268

Full Member level 3

Hi all,

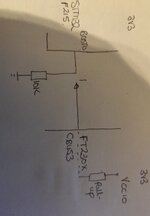

We are trying to use a FT230x CBUS3 to control the BOOT status of a STM32F215.

The boot pin of the STM32 is tied to 0V via a 10K pull down.

The internal pull up of the FT device is used to toggle the boot pin. I have attached a diagram.

We are seeing a voltage of 0.5V which does not meet the requirements for the VIH of the STM32 to register as a logic 1. It has the following criteria 1.75V<VDD<3.6V

However, when the pull down is changed to 100K we get around 2.2V.

I have measured the value of the internal pull up of the FT230 by measuring the current going into the CBUS3 pin and VCcIO is 3.3V. Which is around 66K.

This all makes sense. My question is why when the pull down is at 10K can I still enter boot mode when the voltage going into the STM32 is 0.5V? Sometimes it fails.

Thanks in advance.

We are trying to use a FT230x CBUS3 to control the BOOT status of a STM32F215.

The boot pin of the STM32 is tied to 0V via a 10K pull down.

The internal pull up of the FT device is used to toggle the boot pin. I have attached a diagram.

We are seeing a voltage of 0.5V which does not meet the requirements for the VIH of the STM32 to register as a logic 1. It has the following criteria 1.75V<VDD<3.6V

However, when the pull down is changed to 100K we get around 2.2V.

I have measured the value of the internal pull up of the FT230 by measuring the current going into the CBUS3 pin and VCcIO is 3.3V. Which is around 66K.

This all makes sense. My question is why when the pull down is at 10K can I still enter boot mode when the voltage going into the STM32 is 0.5V? Sometimes it fails.

Thanks in advance.