yefj

Advanced Member level 5

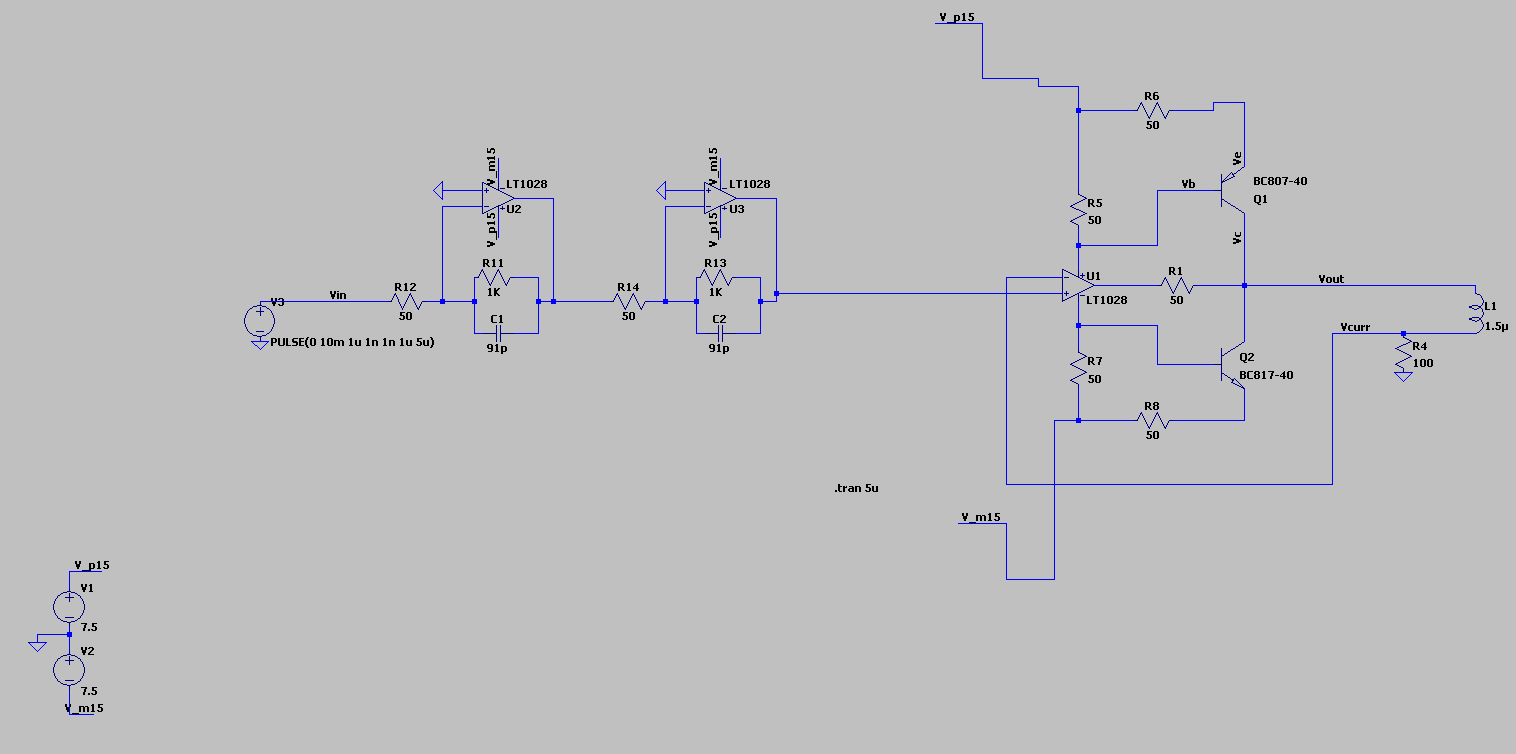

Hello , i have designed with a big help from this forum a driver.

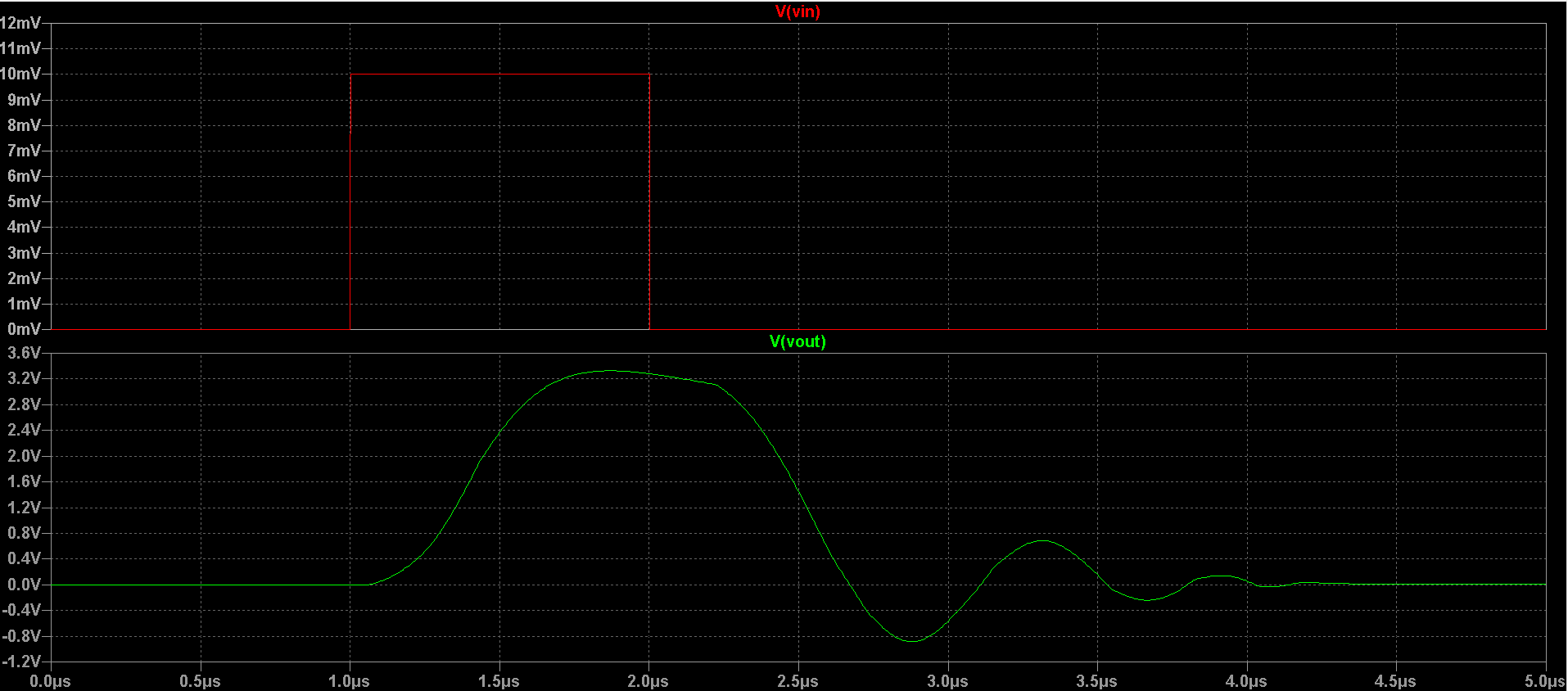

at first glanse it amplified great the signal how ever when i probed R1 resistor as shown below on my lab scope with DC input , i saw oscilations.

Now when i did step responce of the circuilt as shown below i see the oscilations.

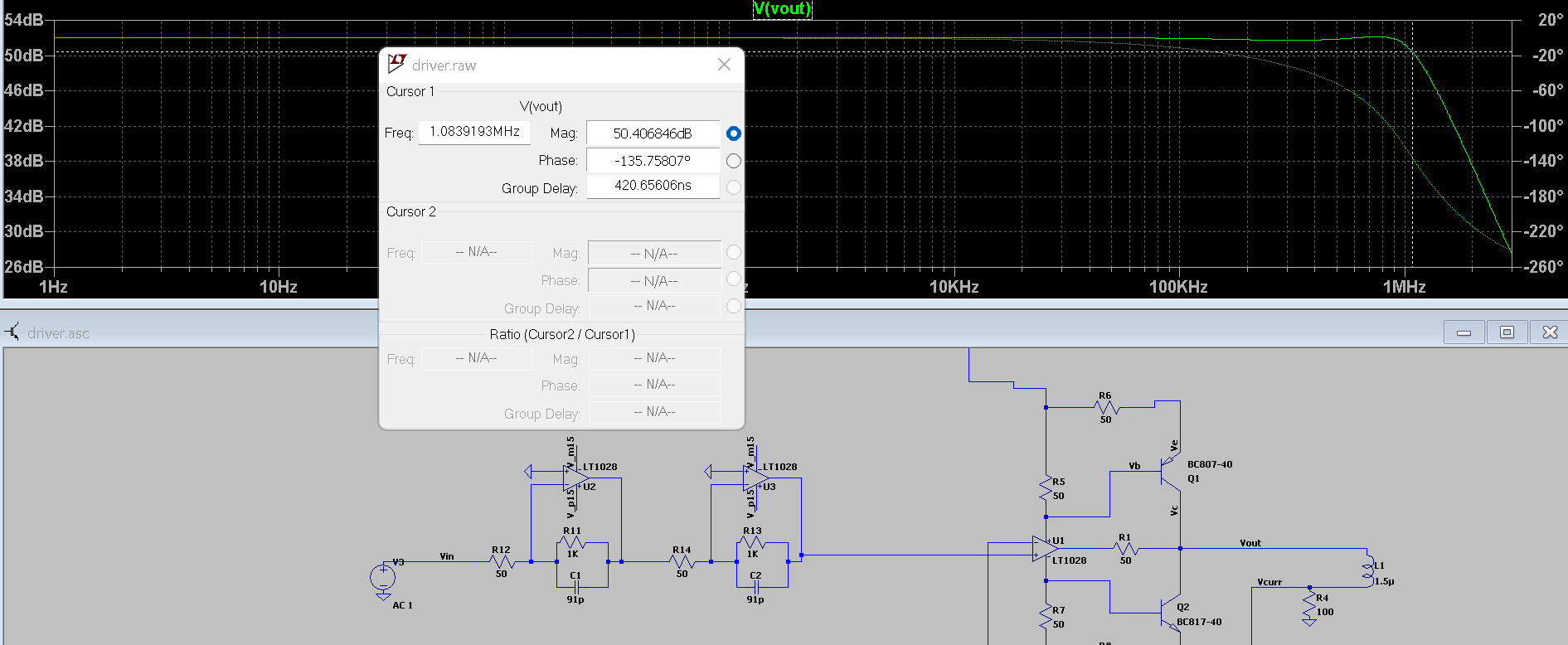

I also know from analog design course that i can try and see the AC responce.

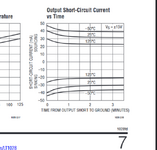

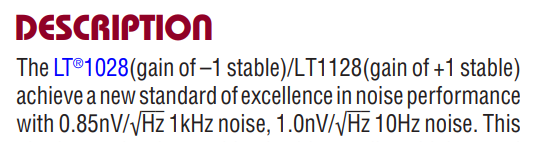

LT1028 is -1 stable ,how does it influence the connection between the stages so i will not get oscilations.

What could cause instability in such configuration?

Thanks.

at first glanse it amplified great the signal how ever when i probed R1 resistor as shown below on my lab scope with DC input , i saw oscilations.

Now when i did step responce of the circuilt as shown below i see the oscilations.

I also know from analog design course that i can try and see the AC responce.

LT1028 is -1 stable ,how does it influence the connection between the stages so i will not get oscilations.

What could cause instability in such configuration?

Thanks.