cupoftea

Advanced Member level 6

Hi,

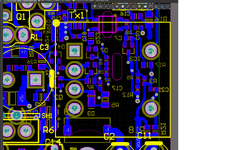

We have an offline , isolated 24W Flyback in an earthed

metal enclosure.

We use TO220 Plastic FET in primary and TO220 plastic

diode at secondary. They are both screwed to the same metal heatsink.

(with no insulation pad)

Then when we apply our 4kVrms (between L+N and output for 2 seconds, it is failing.

Do you believe we need an insulation pad?

When i say its failing, it doesnt indicate failure, but we can hear fizzling at 4kV indicative of breakdown.

The 0-3mA current meter reads no current.

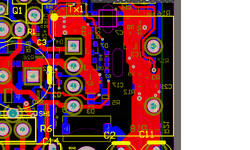

We have an offline , isolated 24W Flyback in an earthed

metal enclosure.

We use TO220 Plastic FET in primary and TO220 plastic

diode at secondary. They are both screwed to the same metal heatsink.

(with no insulation pad)

Then when we apply our 4kVrms (between L+N and output for 2 seconds, it is failing.

Do you believe we need an insulation pad?

When i say its failing, it doesnt indicate failure, but we can hear fizzling at 4kV indicative of breakdown.

The 0-3mA current meter reads no current.