Smillsey

Member level 5

Hello all

I am having problems tracking down the problem with a current source circuit, so I thought I would plot the loop gain and check the gain/phase margins.

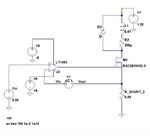

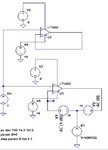

I thought I would first go back to basics and used a guide I found on youtube to plot the loop gain. I am not sure exactly why this method works (using split sources (V1 and V2) and a dependent voltage source (B1), but it does work well and I would rather concentrate my efforts upon understanding the problems with my circuit.

I have attached "loopgain1.asc" which is a test circuit to check the that loop gain measurement method works, I am happy with this test and if you plot the following graph you see the loop gain of the follower circuit;

(I(V2)@1+I(V1)@2)/(I(V1)@1+I(V2)@2)

With a gain margin of 25dB and phase margin of 54 degrees, this circuit is stable.

In my next post I will post up my current source, this may take a few posts - I am sorry about that!

Thanks.

- - - Updated - - -

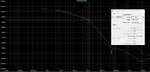

To help any future readers of this thread, I thought I would post a plot of the effects of a capacitive load, in this case 1uF.

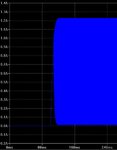

For clarity, the first plot is without the 1uF load and shows no oscillation;

With the 1uF load added, we get into problems;

The reason? Interaction between the output impedance of the op amp (known as Ro) and the capacitive load, which gives rise to another pole in the loop response, this destroys the gain margin we previously had. The loop gain plot now shows +21dB @ 180deg phase shift, this is positive feedback and we have ourselves an oscillator.

Next, I will introduce the current source.

- - - Updated - - -

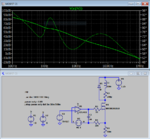

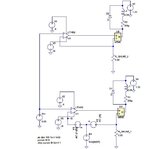

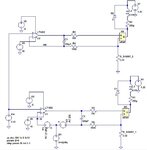

Here is a very basic (with no compensation) current source, it is unstable.

So I perform the same loop gain test, linking the dependent voltage source to be the same voltage at node Vfb

Its an absolute disgrace of a circuit! +72dB @ 180deg phase shift (a big whopping oscillator).

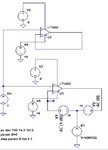

Here is the step response;

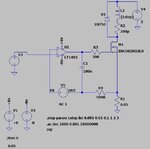

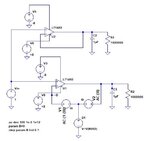

So if I use the stabilising "out of loop" or "in the loop" (can't remember the term) circuit shown here;

https://www.analog.com/media/en/technical-documentation/application-notes/an105fa.pdf

This doesn't work and there is still +75dB @ 180deg phase shift.

The unknown device is the inductor (10mH) + resistor (200uR), the inductance is causing the problem.

The idea of this circuit is to drive a constant current through a highly inductive low resistance load.

Do you have any advice as to how to compensate this loop?

Thanks!

- - - Updated - - -

P.S - I do not need a fast response, so I would be happy rolling off the gain in the loop early, a 10Hz cutoff would be OK.

I am having problems tracking down the problem with a current source circuit, so I thought I would plot the loop gain and check the gain/phase margins.

I thought I would first go back to basics and used a guide I found on youtube to plot the loop gain. I am not sure exactly why this method works (using split sources (V1 and V2) and a dependent voltage source (B1), but it does work well and I would rather concentrate my efforts upon understanding the problems with my circuit.

I have attached "loopgain1.asc" which is a test circuit to check the that loop gain measurement method works, I am happy with this test and if you plot the following graph you see the loop gain of the follower circuit;

(I(V2)@1+I(V1)@2)/(I(V1)@1+I(V2)@2)

With a gain margin of 25dB and phase margin of 54 degrees, this circuit is stable.

In my next post I will post up my current source, this may take a few posts - I am sorry about that!

Thanks.

- - - Updated - - -

To help any future readers of this thread, I thought I would post a plot of the effects of a capacitive load, in this case 1uF.

For clarity, the first plot is without the 1uF load and shows no oscillation;

With the 1uF load added, we get into problems;

The reason? Interaction between the output impedance of the op amp (known as Ro) and the capacitive load, which gives rise to another pole in the loop response, this destroys the gain margin we previously had. The loop gain plot now shows +21dB @ 180deg phase shift, this is positive feedback and we have ourselves an oscillator.

Next, I will introduce the current source.

- - - Updated - - -

Here is a very basic (with no compensation) current source, it is unstable.

So I perform the same loop gain test, linking the dependent voltage source to be the same voltage at node Vfb

Its an absolute disgrace of a circuit! +72dB @ 180deg phase shift (a big whopping oscillator).

Here is the step response;

So if I use the stabilising "out of loop" or "in the loop" (can't remember the term) circuit shown here;

https://www.analog.com/media/en/technical-documentation/application-notes/an105fa.pdf

This doesn't work and there is still +75dB @ 180deg phase shift.

The unknown device is the inductor (10mH) + resistor (200uR), the inductance is causing the problem.

The idea of this circuit is to drive a constant current through a highly inductive low resistance load.

Do you have any advice as to how to compensate this loop?

Thanks!

- - - Updated - - -

P.S - I do not need a fast response, so I would be happy rolling off the gain in the loop early, a 10Hz cutoff would be OK.