yefj

Advanced Member level 5

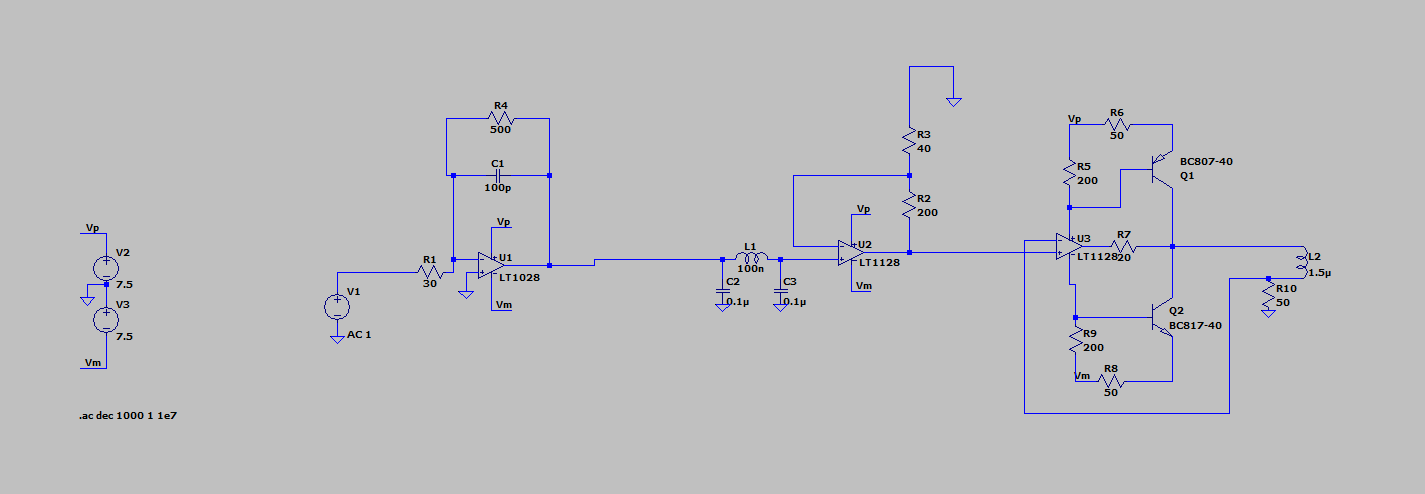

Hello,given the schematics shown below.purely on reducing noise on the output.

Its a very low frequency driver up to 5MHz with noise, pure operating BW is 1Mhz.

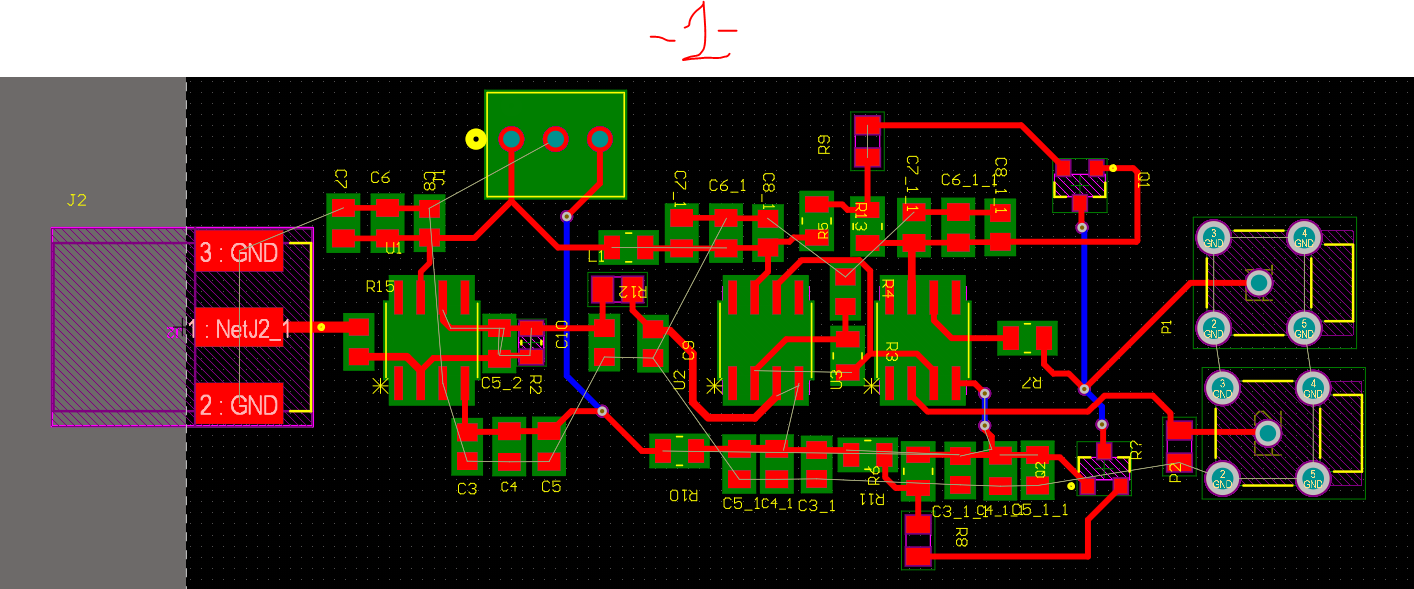

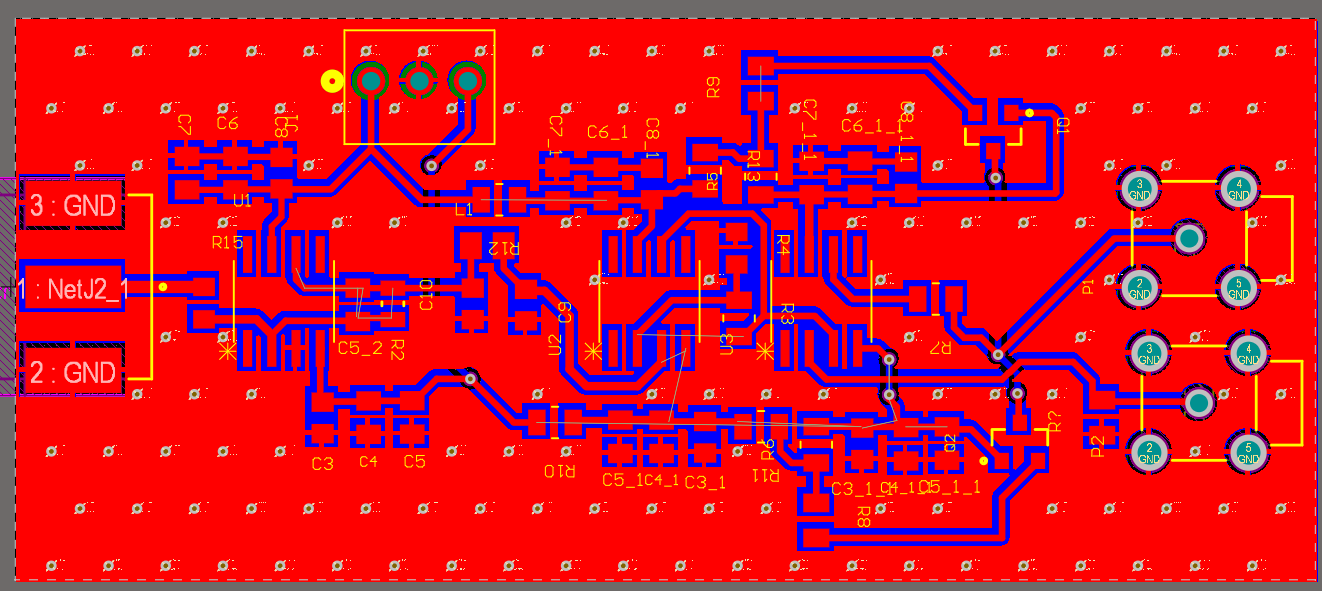

1.As you can see below first i made all the components as dense as possible

2. I put polygon pour and stitching VIAS as shown below.

3. I put 10u 1u 0.1u C0G/NP0 capacitors instead of regular ceramic capacitors and i put then next to the bias Vdd and Vcc on each OPAMP as shown below.

4. I put a pi filter but between the stages but it totally does gain spike in closed loop thus ruins stability so I am thinking to remove it.

5.i put resistor with as much low values a possible to reduce johnson nyquist noise.

Is there more ways you suggest me to improve noise?

Thanks.

Its a very low frequency driver up to 5MHz with noise, pure operating BW is 1Mhz.

1.As you can see below first i made all the components as dense as possible

2. I put polygon pour and stitching VIAS as shown below.

3. I put 10u 1u 0.1u C0G/NP0 capacitors instead of regular ceramic capacitors and i put then next to the bias Vdd and Vcc on each OPAMP as shown below.

4. I put a pi filter but between the stages but it totally does gain spike in closed loop thus ruins stability so I am thinking to remove it.

5.i put resistor with as much low values a possible to reduce johnson nyquist noise.

Is there more ways you suggest me to improve noise?

Thanks.