xeratule

Member level 4

- Joined

- Apr 4, 2009

- Messages

- 69

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,288

- Location

- Istanbul / TURKIYE

- Activity points

- 1,975

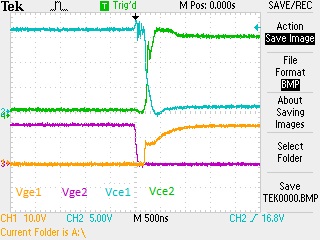

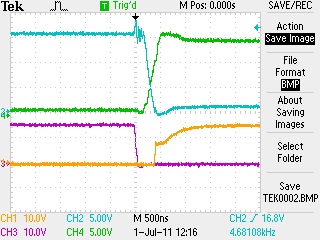

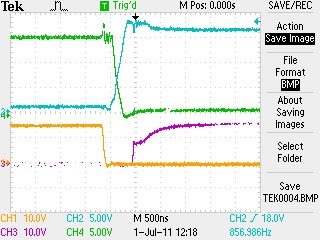

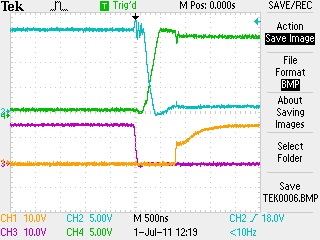

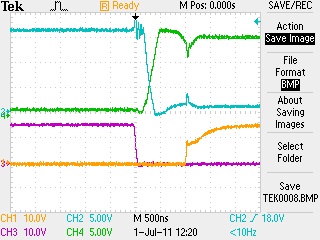

The voltage waveforms are constituted by both transistor and diode operation. In a bridge output with inductive load, the commutation timing is depending on the output current sign. In "active" quadrant, output voltage and current have equal sign, the output is commutating immediately on transistor turn-off and the current transferred to the opposite diode. In "passive" quadrant, output voltage and current have opposite sign, the output is commutating from the diode to the transistor on-turn on.I can't have dead time at collector voltages

So you were driving a resistive load, but still through the transformer, right?In these last waveforms I changed the unstable piezoelectric load with resistance (not pure but close, Z = 43ohms = 41+j13 ohms @ 25khz) capable of handling high currents.

Ideally no, a resistive load won't conduct during the dead time. But your transformer's magnetizing inductance will make it look slightly inductive. That last set of waveforms looks pretty typical (though I think the turn on time is too slow, and the dead time is probably excessive).That's why the waveforms are better. Before driving that unstable resistive+capacitive load I think I should solve my other problems. So does diodes also conduct while the circuit has resistive load?

Shoot through is an independent problem from your load impedance or quadrants or whatever. Shoot through should be solved just by adding dead time to the gate drive. In a good circuit, the gate waveforms should not be affected significantly by the load characteristics. At most you should see slower rise and fall times when operating at higher load current. But if your gate waveform starts seriously distorting or oscillating when you change the load, then something is wrong with the drive circuit and needs to be fixed.Is it bad to be in active quadrant? I mean does the intersection area of the Vce's cause any shoot through or unwanted switching loss? I am confused.

There nothing like good or bad in this regard. Load current waveforms are just an application condition to be considered and usually can't be changed at will. My point was to explain what's going on, I don't see anything dubios in the latest waveforms. You have to assure, that both bridge transistors can't turn on simulataneously, that seems no problem at present.Is it bad to be in active quadrant? I mean does the intersection area of the Vce's cause any shoot through or unwanted switching loss?

I neither have the transformer nor the capacitor in those waveforms, just the resistive load.So you were driving a resistive load, but still through the transformer, right?

A pure resistive load won't cause the output current to commutate to the diode on it's own. There must be at least some circuit inductance to get the shown waveforms.I neither have the transformer nor the capacitor in those waveforms, just the resistive load.

We use cookies and similar technologies for the following purposes:

Do you accept cookies and these technologies?

We use cookies and similar technologies for the following purposes:

Do you accept cookies and these technologies?