- Joined

- Jan 22, 2008

- Messages

- 53,108

- Helped

- 14,792

- Reputation

- 29,871

- Reaction score

- 14,291

- Trophy points

- 1,393

- Location

- Bochum, Germany

- Activity points

- 301,064

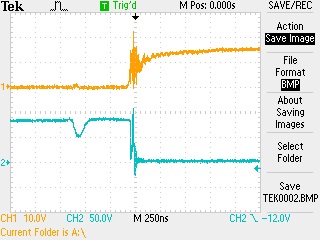

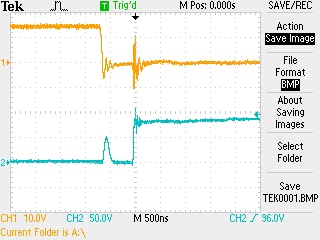

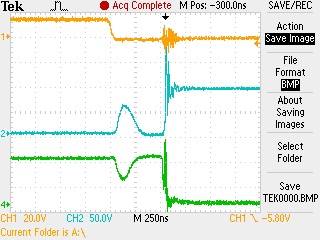

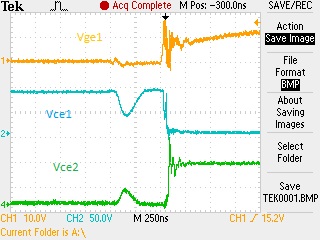

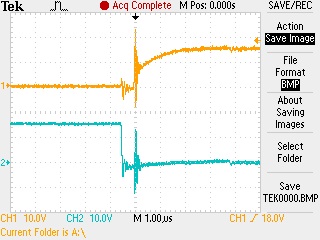

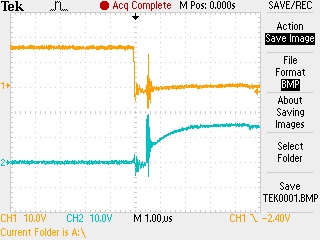

Strictly spoken, the schottky diode's purpose isn't faster turn off rather than keeping the gate voltage safely low when the other switch turns on. The most reliable way to achieve this would be a bipolar gate driver supply. I won't mind the negative overshoot, if you feel that the negative driver current is too high, you could use asymmetrical resistors, e.g. 5 - 10 ohm RD series circuit for turn off, 50 ohm for turn on.

Snubbers are needed, if transient overvoltages become dangerous for the involved devices, or to reduce interference emissions. They will rarely reduce semiconductor losses but add some losses on their own. In a good, low inductance H-bridge design, snubbers should be superfluous.

Snubbers are needed, if transient overvoltages become dangerous for the involved devices, or to reduce interference emissions. They will rarely reduce semiconductor losses but add some losses on their own. In a good, low inductance H-bridge design, snubbers should be superfluous.