doncarlosalbatros

Full Member level 2

For minimizing SMPS ripple and especially noise, I’m trying to make a small interface which is a post regulator cascaded after an LC filter. I have come across some papers related to this topic and the idea is to establish good noise rejection by using a low drop out LDO regulator for frequencies lower than like 100 kHz and for higher frequencies by using an LC filter. At this video it also gives a very nice example at around 2:56.

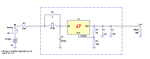

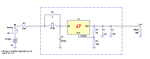

The topology can be seen in the circuit I have drawn in LTspice. Here is my circuit in question(the one inside the dashed box is the filter):

The circuit is set for 120mA load with 12V regulator output to a 15V input.

Now my biggest problem in simulation was that since I don't know the DC output resistance R3 of an SMPS and it can be different for any different SMPS. So for the worst case I took it as 0.02 Ohm. I say worst case because for the LC filter this doesn’t prevent the resonance problem. So to prevent the LC resonance, I added a parallel 1 Ohm resistor R1 with the inductor L1. In simulation L1 and C2 forms a very nice high freq. filter. Then I use this LT1086 as an LDO. Here is its datasheet and in applications it is mentioned that it is also recommended for SMPS switching noise filtering(it says "Post Regulators for Switching Supplies"). R2 and Rp set the output to around 12V for a 15V input. Rp can be a potentiometer to fine-tune the output voltage. According to the datasheet if I’m not mistaken the C1 is needed to be a tantalum capacitor and C3 is a ceramic capacitor both with low ESR.

Now I have made transient analysis in LTspice for this filter where the input is 15VDC with 1V pulse noise (with 10p rising falling edges) superimposed on it. So I repeated the same procedure for different noise pulse frequencies 50Hz, 100Hz, 1kHz, 100kHz, 1MegHz.

Below are the simulation results for input and output for these frequencies:

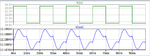

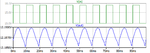

At 50Hz:

At 100Hz:

At 1kHz:

At 100kHz:

At 1MegHz:

The results are peak to peak amplitudes at the output for 1V pulse input noise at different frequencies. And here are the results for each:

50Hz ------> 1.6mV

100Hz -----> 3.8mV

1kHz ------> 173uV

100kHz ----> 41uV

1MegHz -----> 1uV

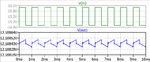

Here is the power dissipation for the regulator which is around 0.5W:

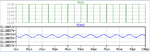

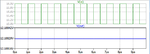

And finally here below is the current drawn from the SMPS and flow through input stage:

My questions are:

How can I reduce this supply current? Apparently it is 6A. Obviously there is something wrong with this even though the filtering is fine.

I would be glad to hear any other recommendations for this circuit. SMSP cannot handle more than 500mA or maybe 1A, so reducing C2 can be an option but that degrades the filtering. Or am I exaggerating the 1V noise?

The topology can be seen in the circuit I have drawn in LTspice. Here is my circuit in question(the one inside the dashed box is the filter):

The circuit is set for 120mA load with 12V regulator output to a 15V input.

Now my biggest problem in simulation was that since I don't know the DC output resistance R3 of an SMPS and it can be different for any different SMPS. So for the worst case I took it as 0.02 Ohm. I say worst case because for the LC filter this doesn’t prevent the resonance problem. So to prevent the LC resonance, I added a parallel 1 Ohm resistor R1 with the inductor L1. In simulation L1 and C2 forms a very nice high freq. filter. Then I use this LT1086 as an LDO. Here is its datasheet and in applications it is mentioned that it is also recommended for SMPS switching noise filtering(it says "Post Regulators for Switching Supplies"). R2 and Rp set the output to around 12V for a 15V input. Rp can be a potentiometer to fine-tune the output voltage. According to the datasheet if I’m not mistaken the C1 is needed to be a tantalum capacitor and C3 is a ceramic capacitor both with low ESR.

Now I have made transient analysis in LTspice for this filter where the input is 15VDC with 1V pulse noise (with 10p rising falling edges) superimposed on it. So I repeated the same procedure for different noise pulse frequencies 50Hz, 100Hz, 1kHz, 100kHz, 1MegHz.

Below are the simulation results for input and output for these frequencies:

At 50Hz:

At 100Hz:

At 1kHz:

At 100kHz:

At 1MegHz:

The results are peak to peak amplitudes at the output for 1V pulse input noise at different frequencies. And here are the results for each:

50Hz ------> 1.6mV

100Hz -----> 3.8mV

1kHz ------> 173uV

100kHz ----> 41uV

1MegHz -----> 1uV

Here is the power dissipation for the regulator which is around 0.5W:

And finally here below is the current drawn from the SMPS and flow through input stage:

My questions are:

How can I reduce this supply current? Apparently it is 6A. Obviously there is something wrong with this even though the filtering is fine.

I would be glad to hear any other recommendations for this circuit. SMSP cannot handle more than 500mA or maybe 1A, so reducing C2 can be an option but that degrades the filtering. Or am I exaggerating the 1V noise?

Last edited: