Praveen_Raj

Newbie level 5

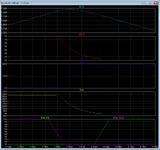

I'm trying compare the efficiency of an inverter (power R1 / input Power) at different switching frequencies to understand switching losses, but im getting the same efficiency of 95.4% when Fs = 10 and Fs= 100k.

I'm using Mosfets with Vds = 600V

Can someone please help me understand why this is happening....

I'm using Mosfets with Vds = 600V

Can someone please help me understand why this is happening....