Saltwater

Member level 4

- Joined

- Aug 30, 2015

- Messages

- 79

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Activity points

- 1,951

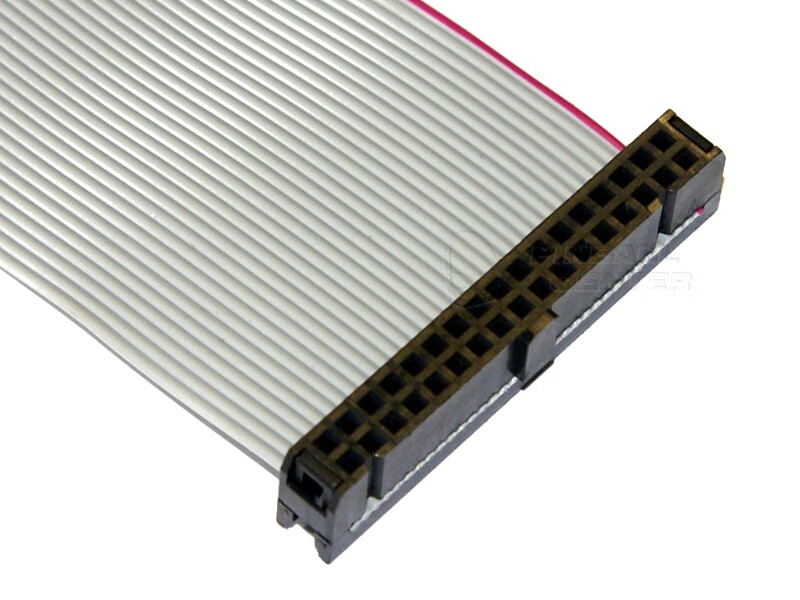

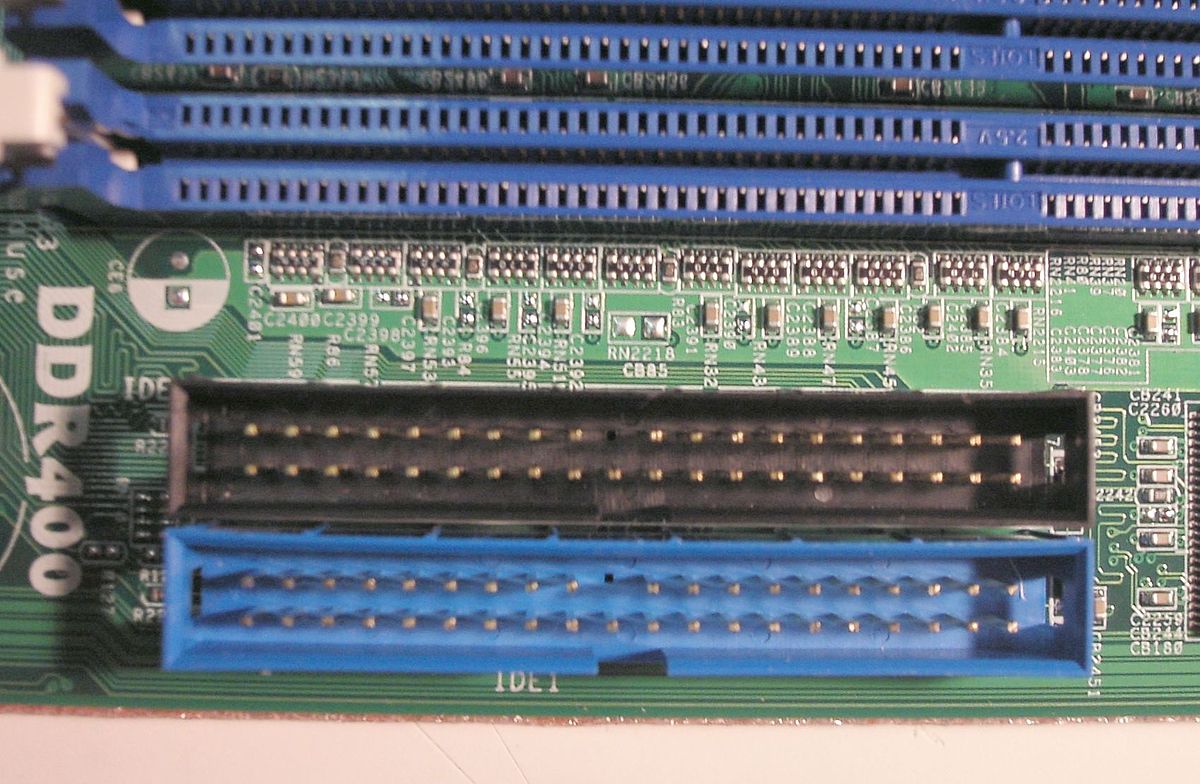

Not grounding the ribbon cable will result in very large ground loops as the signals crossing over the ribbon cable will have NO return path except through your power supply ground.

I'm not sure you are reading good papers on grounding if they suggest doing what you seem to be proposing.

To avoid miscommunicating.. Not to be stubborn, im really trying to learn here.

aesthetically I would prefer to do this. In the light of the papers I feel this would not be terribly wrong?

Last edited: