JMG

Member level 3

Yes I am aware of the 60V breakdown voltage. It was a mistake as I assumed the voltage across the diode would never rise above the max input voltage. Even so at 22 - 27Vin and 26Vled, that is still a maximum of 53V. I don't think this is causing the circuit to fail at these lower input voltages. Also remember, that the circuit works at these low input voltages if the output current is lowered to 5A which equates to Vled of about 23V.

There are 2 diodes in the one package, thus there are 2 diodes in the circuit. Layout is per the schematic. That diode does get warm but there is a massive heat sink that is attached to both FET's and the diode. I may put another diode package in there also. What is the general feeling on paralleling up diodes in this situation?

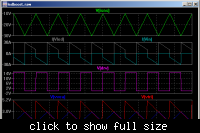

I am still not sure why the duty cycle goes above 55 or 57%. That should be the maximum but it looks like it goes to 99% before it trips into hiccup mode.

There are 2 diodes in the one package, thus there are 2 diodes in the circuit. Layout is per the schematic. That diode does get warm but there is a massive heat sink that is attached to both FET's and the diode. I may put another diode package in there also. What is the general feeling on paralleling up diodes in this situation?

I am still not sure why the duty cycle goes above 55 or 57%. That should be the maximum but it looks like it goes to 99% before it trips into hiccup mode.