cupoftea

Advanced Member level 6

Hi,

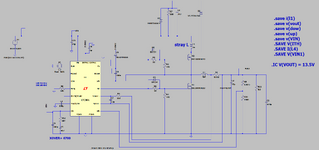

Would you agree that the following spec is too high in power and Vin for a Dual

Synchronous Buck solution at 450kHz (each Buck at 450kHz)…

27Vin

13.5Vout

30A out.(405W)

No isolation needed.

This is too much for a Dual Synchronous Buck with each 202W Buck stage switching at 450kHz.

The synchronous Buck at high switching frequency is really meant for high duty cycle ratios

where Vin is low and Vout very low (eg 9V to 1V5). And Iout 20A or less even then.

For hard switching above a certain power level, then transformer isolated topologies become

more suitable, as the leakage reset automatically recycles the leakage current back to the input...eg in a Full Bridge.

Also, a Buck at 27Vin and 202W and 450kHz is pushing it. In the Buck, when the top FET Turns OFF, there is a lot of

energy stored in the strays of the input caps and traces, and even good layout cannot avoid this, and it creates serious

overvoltage problems on the top FET.

Would you agree this spec is not for a Dual Sync Buck at 450kHz?

Would you agree that the following spec is too high in power and Vin for a Dual

Synchronous Buck solution at 450kHz (each Buck at 450kHz)…

27Vin

13.5Vout

30A out.(405W)

No isolation needed.

This is too much for a Dual Synchronous Buck with each 202W Buck stage switching at 450kHz.

The synchronous Buck at high switching frequency is really meant for high duty cycle ratios

where Vin is low and Vout very low (eg 9V to 1V5). And Iout 20A or less even then.

For hard switching above a certain power level, then transformer isolated topologies become

more suitable, as the leakage reset automatically recycles the leakage current back to the input...eg in a Full Bridge.

Also, a Buck at 27Vin and 202W and 450kHz is pushing it. In the Buck, when the top FET Turns OFF, there is a lot of

energy stored in the strays of the input caps and traces, and even good layout cannot avoid this, and it creates serious

overvoltage problems on the top FET.

Would you agree this spec is not for a Dual Sync Buck at 450kHz?