userx2

Full Member level 3

Hello,

I am scratching my head again regarding grounding of digital and analogue parts

I have split ground planes for digital ground DGND and analogue ground AGND, joining only at the power supply regulator.

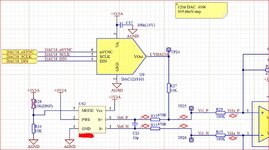

I now have a DAC DAC121S101 chip that will supply a voltage into an analogue circuit as shown.

Should that chip be grounded to DGND or AGND? I think AGND is correct since the chip supplies a precision voltage onto the analog circuit.

Datasheet: https://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&gotoUrl=https://www.ti.com/lit/gpn/dac121s101

But then what about the return currents of the digital lines? They will have to cross the split ground planes.

Should I add series resistors to those? Or do I have it completely wrong?

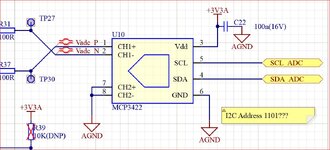

Likewise, on the other side of this circuit, I have an ADC chip MCP3422. I have the same guestion here regarding the power and grounding.

Datasheet: https://ww1.microchip.com/downloads/en/DeviceDoc/22088c.pdf

The ADC Datasheet mentions the grounding in section 3.2 but I do not understand what that means in practice.

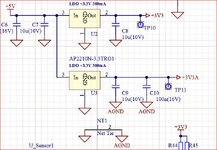

The preliminary PCB layout is also shown. The green lines show the power plane split for the AVDD but the ground plane has the same split (brown lines barely visible under green lines) This is a 4 layer PCB.

I am scratching my head again regarding grounding of digital and analogue parts

I have split ground planes for digital ground DGND and analogue ground AGND, joining only at the power supply regulator.

I now have a DAC DAC121S101 chip that will supply a voltage into an analogue circuit as shown.

Should that chip be grounded to DGND or AGND? I think AGND is correct since the chip supplies a precision voltage onto the analog circuit.

Datasheet: https://www.ti.com/general/docs/suppproductinfo.tsp?distId=10&gotoUrl=https://www.ti.com/lit/gpn/dac121s101

But then what about the return currents of the digital lines? They will have to cross the split ground planes.

Should I add series resistors to those? Or do I have it completely wrong?

Likewise, on the other side of this circuit, I have an ADC chip MCP3422. I have the same guestion here regarding the power and grounding.

Datasheet: https://ww1.microchip.com/downloads/en/DeviceDoc/22088c.pdf

The ADC Datasheet mentions the grounding in section 3.2 but I do not understand what that means in practice.

The preliminary PCB layout is also shown. The green lines show the power plane split for the AVDD but the ground plane has the same split (brown lines barely visible under green lines) This is a 4 layer PCB.