T

treez

Guest

thanks, there are loads out there, but above 27Amps and there are few in stock on digikey or farnell. I reckon there will be constant supply issues.

Actually, Many Thanks to Sunnyskyguy who solved this thread inadvertently a few weeks back...Sunnyskyguy pointed out that ETD/efd etc cores, if not expensively lapped, have dramatically reduced permeability. (Also, if the cores are not properly mated with a custom jig, then the same again).

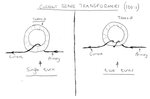

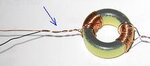

This potential massive reduction in etd core permeability, can mean far more secondary magnetising current than wanted, meaning signal distortion........I see now that unless expensive jigs and lapped cores are available, torroids are the only way to go for CSTs.

Thread #8 of this shows Sunnyskyguys great solution to this problem.....torroids are the way forward..

https://www.edaboard.com/threads/341980/

Actually, Many Thanks to Sunnyskyguy who solved this thread inadvertently a few weeks back...Sunnyskyguy pointed out that ETD/efd etc cores, if not expensively lapped, have dramatically reduced permeability. (Also, if the cores are not properly mated with a custom jig, then the same again).

This potential massive reduction in etd core permeability, can mean far more secondary magnetising current than wanted, meaning signal distortion........I see now that unless expensive jigs and lapped cores are available, torroids are the only way to go for CSTs.

Thread #8 of this shows Sunnyskyguys great solution to this problem.....torroids are the way forward..

https://www.edaboard.com/threads/341980/

Last edited by a moderator: