Shady Ahmed

Member level 5

Unfortunately , i couldn't use the IDEAL switches.

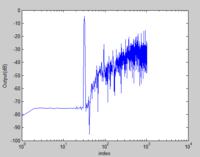

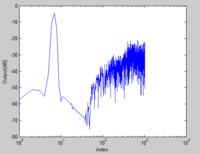

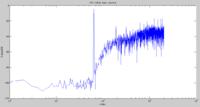

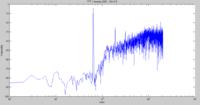

Ideal switches from analogLib cause large spikes, at CLK transision , when the current should turn from zero to 350uA , it causes a spike about 2 or 3 mA .

So , even when using the IDEAL Switch , the total SNR is nearly the same.

I also tried designing the DAC with switches in SAT region , there is no luck too, SNR may have improved a few dB 's but still, not good.

I don't know what is the problem that i can't see, since that i am sure that Current Steering DAC could work with even higher frequencies than 384 MHz.

Any more help ??

Ideal switches from analogLib cause large spikes, at CLK transision , when the current should turn from zero to 350uA , it causes a spike about 2 or 3 mA .

So , even when using the IDEAL Switch , the total SNR is nearly the same.

I also tried designing the DAC with switches in SAT region , there is no luck too, SNR may have improved a few dB 's but still, not good.

I don't know what is the problem that i can't see, since that i am sure that Current Steering DAC could work with even higher frequencies than 384 MHz.

Any more help ??