adnan012

Advanced Member level 1

- Joined

- Oct 6, 2006

- Messages

- 468

- Helped

- 2

- Reputation

- 4

- Reaction score

- 2

- Trophy points

- 1,298

- Activity points

- 4,923

Hi,

I am working on a super-capacitor bank charger. The specs are

Super Capacitor Bank 100F/15V

Charging time required 60 seconds

Input voltage 18V

Max Charging voltage 15V

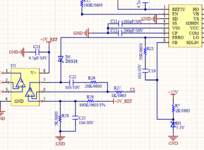

I am using a synchronous buck with constant current (maximum) loop + CV loop. At startup the charging current is 40A. As the capacitor voltage start rising the charging current starts decreasing. After 60 seconds the 15V at capacitor bank is achieved, at this point current maximum current was 20A. its decreases from 40A to 20A linearly. At startup the PWM on time at high side MOSFET gate is very small and it starts growing as the charge builds up on the capacitor.

I want to know why the current does not stay at 40A through out the charging process. All temperatures are in limits.

Best Regards

I am working on a super-capacitor bank charger. The specs are

Super Capacitor Bank 100F/15V

Charging time required 60 seconds

Input voltage 18V

Max Charging voltage 15V

I am using a synchronous buck with constant current (maximum) loop + CV loop. At startup the charging current is 40A. As the capacitor voltage start rising the charging current starts decreasing. After 60 seconds the 15V at capacitor bank is achieved, at this point current maximum current was 20A. its decreases from 40A to 20A linearly. At startup the PWM on time at high side MOSFET gate is very small and it starts growing as the charge builds up on the capacitor.

I want to know why the current does not stay at 40A through out the charging process. All temperatures are in limits.

Best Regards