hesam_ahmadi

Junior Member level 1

Hi all,

I draw layout of a Buried Double Junction(BDJ) Photo detector and create corresponding schematic too.

I've put two diode recognition layer in layout but when i do a LVS check, only one diode is recognized.

any suggestions about why only one diode is recognized?

BDJ cross section:

schematic:

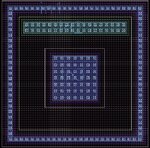

Layout:

Thanks for your answers

I draw layout of a Buried Double Junction(BDJ) Photo detector and create corresponding schematic too.

I've put two diode recognition layer in layout but when i do a LVS check, only one diode is recognized.

any suggestions about why only one diode is recognized?

BDJ cross section:

schematic:

Layout:

Thanks for your answers