Bjtpower_magic

Full Member level 1

Hi,

One of my project, ex colleague used AD7693 ADC Converter (https://www.analog.com/media/en/technical-documentation/data-sheets/AD7693.pdf)

i am new to ADC and i need few clarifications.

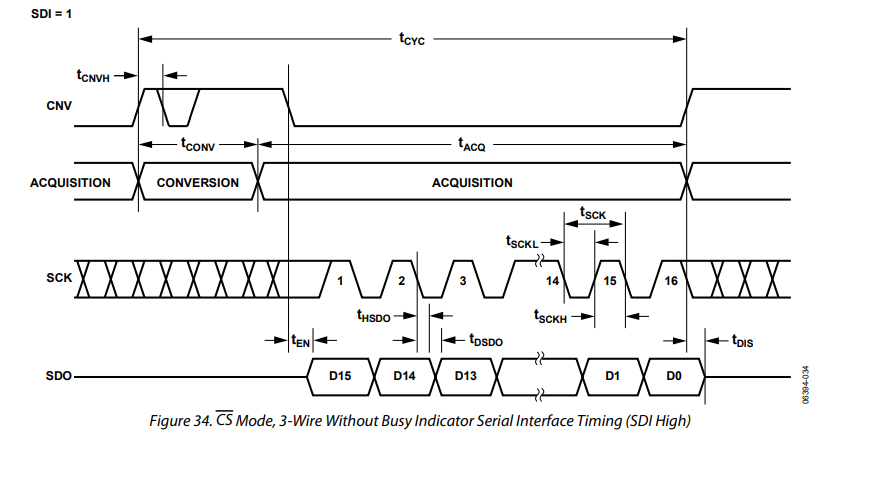

Since it mentioned that it has sampling rate of 500KSPS but i fail to understand how timing diagram.

Please help me in understanding my assumptions.

1) We have TCYC=2uS=500 KHZ

2) We have TSCK=15nS=66 MHZ

So for each cycle of 66MHZ, it will sample 1 bit so in total for 16bits it will take 16*tsck=16*15=240nS?

So for 1 second, i will have 16bits/240nS=66M bits so my question is how is relation of 500KSPS?

Can you please help me understanding relations?

One of my project, ex colleague used AD7693 ADC Converter (https://www.analog.com/media/en/technical-documentation/data-sheets/AD7693.pdf)

i am new to ADC and i need few clarifications.

Since it mentioned that it has sampling rate of 500KSPS but i fail to understand how timing diagram.

Please help me in understanding my assumptions.

1) We have TCYC=2uS=500 KHZ

2) We have TSCK=15nS=66 MHZ

So for each cycle of 66MHZ, it will sample 1 bit so in total for 16bits it will take 16*tsck=16*15=240nS?

So for 1 second, i will have 16bits/240nS=66M bits so my question is how is relation of 500KSPS?

Can you please help me understanding relations?