AdvaRes

Advanced Member level 4

gaom9 said:

Hi, I can't see figures could you please upload again ?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

gaom9 said:

gaom9 said:Hi,

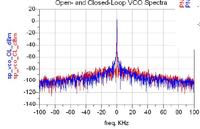

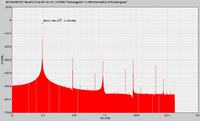

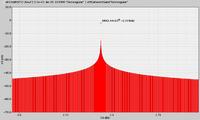

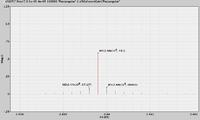

I am running the total simulation of the Frequency Synthesizers with the Analog circuit in transistor level.

I set a tighter tolerances, reltol 1e-5, vabsto 3e-8 iabstol 1e-13 Method gear2only and errpreset=conservative. I find it cost a quite long time to do so, I want to do a 100uS tran simulaiton, but after 12 hours, it only simulation to 1.3us, so it will cost about 50days to finish it...

Is there any method to reduce the simulation time, please?

Thank you!

Best regards!