ivan_mateo

Member level 1

Hello everyone,

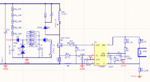

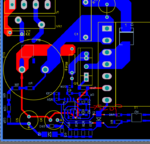

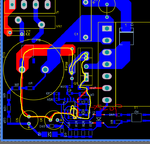

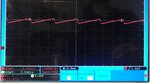

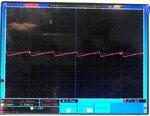

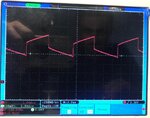

I design a simple flyback converter and assemby in PCB. My transformer etd29, primary indutance around 400uH and 40Turn, secondary is 9Turn. But when I drive UC3845 around 10V y applying external voltage from power supply not from line. There is some oscillaiton in PWM signal, as you can see in my attachment. Can anybody commet this issue? f=100kHz

I design a simple flyback converter and assemby in PCB. My transformer etd29, primary indutance around 400uH and 40Turn, secondary is 9Turn. But when I drive UC3845 around 10V y applying external voltage from power supply not from line. There is some oscillaiton in PWM signal, as you can see in my attachment. Can anybody commet this issue? f=100kHz