ueckid

Member level 1

- Joined

- Mar 22, 2017

- Messages

- 39

- Helped

- 2

- Reputation

- 4

- Reaction score

- 3

- Trophy points

- 1,288

- Location

- Osaka, Japan

- Activity points

- 1,692

Hi all,

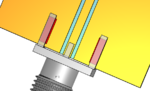

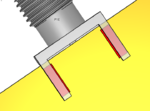

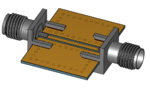

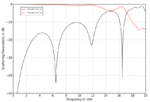

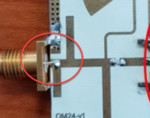

Could anyone please tell me how to remove SMA connector-Microstrip transition for large-signal measurement of a PA? In measurement, I noticed that this transition will shift the optimum load impedance seen by Transistor and therefore degrading the output power, gain and efficiency of my PA designed at 2.4 GHz. In measurement the measured power is lower than simulation by about 3 dB.

Please see figure below.

I wonder how I can tune load/source impedance in practice to compensate this impedance shift?

Could anyone please tell me how to remove SMA connector-Microstrip transition for large-signal measurement of a PA? In measurement, I noticed that this transition will shift the optimum load impedance seen by Transistor and therefore degrading the output power, gain and efficiency of my PA designed at 2.4 GHz. In measurement the measured power is lower than simulation by about 3 dB.

Please see figure below.

I wonder how I can tune load/source impedance in practice to compensate this impedance shift?