Junus2012

Advanced Member level 5

Dear friends,

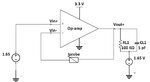

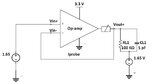

Some friends suggested me to use the stability analyses from cadence to get the AC parameters of my amplifier (DC gain, GBW, PM)

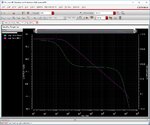

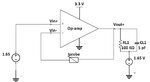

The simulation setup is as I attached it below, as you can see that the circuit is provided only with DC, then I run the STB simulation and using the Iprobe as the instance. After running the simulation I can get all the required parameters,

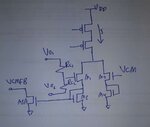

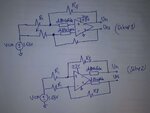

My question here, when I measure the AC parameters from the open loop gain (the classical simulation setup) I have to be very careful to compensate for the input offset voltage, otherwise my setup can easily fail,

However from the STB analyses I can see it is closed loop feedback so I think there is no need for warring about the offset voltage compensation,

Please confirm me if it is right,

Such a property is very important for me when I want to simulate the DC gain over the entire range of the input common mode voltage. Such kind of simulation if I would perform by using the classical open loop setup it will not be accurate because the offset voltage also can change with the input voltage range.

My second question please, Does the STB result has good accuracy and can it be depended ?

Thank you very much in advance

Some friends suggested me to use the stability analyses from cadence to get the AC parameters of my amplifier (DC gain, GBW, PM)

The simulation setup is as I attached it below, as you can see that the circuit is provided only with DC, then I run the STB simulation and using the Iprobe as the instance. After running the simulation I can get all the required parameters,

My question here, when I measure the AC parameters from the open loop gain (the classical simulation setup) I have to be very careful to compensate for the input offset voltage, otherwise my setup can easily fail,

However from the STB analyses I can see it is closed loop feedback so I think there is no need for warring about the offset voltage compensation,

Please confirm me if it is right,

Such a property is very important for me when I want to simulate the DC gain over the entire range of the input common mode voltage. Such kind of simulation if I would perform by using the classical open loop setup it will not be accurate because the offset voltage also can change with the input voltage range.

My second question please, Does the STB result has good accuracy and can it be depended ?

Thank you very much in advance