fouwad

Full Member level 4

Hi, I am designing a Data Acquisition System for RTDs, for which i used this application note for analog part. ww1.microchip.com/downloads/en/appnotes/00687c.pdf

I used ADA4004-2 Op Amps instead of MCP609. The application note used 7.47 Gain V/V while i used 8V/V. Moreover, i added another Gain stage(just simple non inverting Gain) after the Filter+Gain stage. The Gain value for next stage is 2.5-5V/V.

Now the issue is that the Op-Amp used in SallenKey+Gain configuration keeps on malfunctioning after some time or is permanently damaged giving saturated value of +15V or -15V. When i replace this OpAmp, new one starts working fine until it faces the fate of the old one.

I would like to add one more thing that i am multiplexing the RTDs and the unconnected ones produce a saturated value at the output, can this be the reason of short life of my OpAmps

- - - Updated - - -

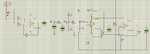

This is the image of the Circuit from Application Note

I used ADA4004-2 Op Amps instead of MCP609. The application note used 7.47 Gain V/V while i used 8V/V. Moreover, i added another Gain stage(just simple non inverting Gain) after the Filter+Gain stage. The Gain value for next stage is 2.5-5V/V.

Now the issue is that the Op-Amp used in SallenKey+Gain configuration keeps on malfunctioning after some time or is permanently damaged giving saturated value of +15V or -15V. When i replace this OpAmp, new one starts working fine until it faces the fate of the old one.

I would like to add one more thing that i am multiplexing the RTDs and the unconnected ones produce a saturated value at the output, can this be the reason of short life of my OpAmps

- - - Updated - - -

This is the image of the Circuit from Application Note