alftel

Member level 1

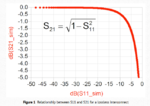

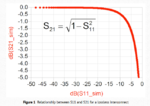

Thanks a lot again Volker! I guess data is good enough to try it on PCB (I am looking at https://www.edn.com/electronics-blo...ch-return-loss-is-too-much--Rule-of-Thumb--12 as a reference for S11 vs S21 as below). As for trace width - I double checked with all CPWG Ground calculators available and all of them show impedance in a range 50-51 Ohm for FR4 0.6mm, two layer, 0.65mm trace width, 0.2mm gap, so can I assume that this is FR4 substrate contributes to S11 (path from input port to the first resistor)?

THANKS AGAIN!

- - - Updated - - -

Thanks a lot Volker! Data looks good - I am using the following reference ( https://www.edn.com/electronics-blo...ch-return-loss-is-too-much--Rule-of-Thumb--12 ) to get a sense how much S11 is too much (see graph below), and based on this data 8-port design has a good chance to be implemented. As for trace width (quote: "According to my simulation the line width isn't correct, this is what I get for the path from input port to the first resistor" ), I double checked with all available CPWG Ground calculators, and looks like my calculation is correct - for two layer 0.6mm FR4 with 0.51mm substrate height, trace 0.65mm and gap 0.2mm CPWG Ground shows 50-51 Ohm impedance, so it's probably FR4 contributing to S11 the most (I guess). I will go ahead and order PCBs for both designs and see how it will perform in real world. Just in case you will have a chance to try my 12 port stuff - it will be really appreciated. Good stuff! Thanks again!

THANKS AGAIN!

- - - Updated - - -

Thanks a lot Volker! Data looks good - I am using the following reference ( https://www.edn.com/electronics-blo...ch-return-loss-is-too-much--Rule-of-Thumb--12 ) to get a sense how much S11 is too much (see graph below), and based on this data 8-port design has a good chance to be implemented. As for trace width (quote: "According to my simulation the line width isn't correct, this is what I get for the path from input port to the first resistor" ), I double checked with all available CPWG Ground calculators, and looks like my calculation is correct - for two layer 0.6mm FR4 with 0.51mm substrate height, trace 0.65mm and gap 0.2mm CPWG Ground shows 50-51 Ohm impedance, so it's probably FR4 contributing to S11 the most (I guess). I will go ahead and order PCBs for both designs and see how it will perform in real world. Just in case you will have a chance to try my 12 port stuff - it will be really appreciated. Good stuff! Thanks again!