palmeiras

Full Member level 6

- Joined

- Feb 22, 2010

- Messages

- 375

- Helped

- 61

- Reputation

- 122

- Reaction score

- 50

- Trophy points

- 1,308

- Location

- South America

- Activity points

- 4,199

Hi guys!

Have anybody faced this problem before?

I´ve read some other threads but I didn’t get the solution yet.

I´m using IBM technology and it has the substrate contact "subc".

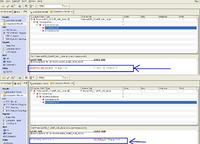

I´ve designed an inverter and it does not present any error of DRC and LVS (100% clean). However when I´ve designed another cell composed by two inverters, the LVS does not pass. Why?

Because in the layout: all GND pins and subc contacts are connected together. But this connection is not possible in the schematic when each inverter cell has its own subc, and I cannot connect these substrate contacts in parallel.

Does anyone have a recommendation to overcome this issue?

Thanks in advance,

Have anybody faced this problem before?

I´ve read some other threads but I didn’t get the solution yet.

I´m using IBM technology and it has the substrate contact "subc".

I´ve designed an inverter and it does not present any error of DRC and LVS (100% clean). However when I´ve designed another cell composed by two inverters, the LVS does not pass. Why?

Because in the layout: all GND pins and subc contacts are connected together. But this connection is not possible in the schematic when each inverter cell has its own subc, and I cannot connect these substrate contacts in parallel.

Does anyone have a recommendation to overcome this issue?

Thanks in advance,