allennlowaton

Full Member level 5

Hello EDA fellows,

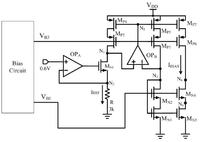

I have been doing this Ibias generator circuit recently.

The circuit is shown below.

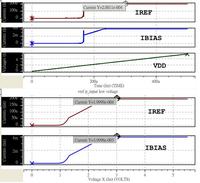

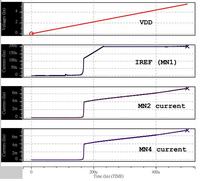

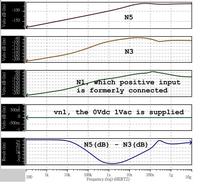

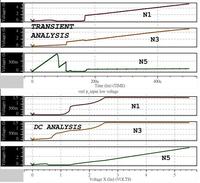

The figure below shows the transient and DC analyses results.

I can't understand why they're not the same.

DC Analysis provides constant current all throughout the desired range

but the transient is increasing. The two simulations share the same simulation paramaters.

Thank you for spending your precious time on this.

I have been doing this Ibias generator circuit recently.

The circuit is shown below.

The figure below shows the transient and DC analyses results.

I can't understand why they're not the same.

DC Analysis provides constant current all throughout the desired range

but the transient is increasing. The two simulations share the same simulation paramaters.

Thank you for spending your precious time on this.